# SERVICE MANUAL & TROUBLESHOOTING GUIDE FOR

7521

BY: Jesse .Jan

TESTING TECHNOLOGY DEPARTMENT / TSSC

MAR. 2001

# **CONTENTS**

| 1. HARDWARE ENGINEERING SPECIFICATION         | <b>P.2</b>  |

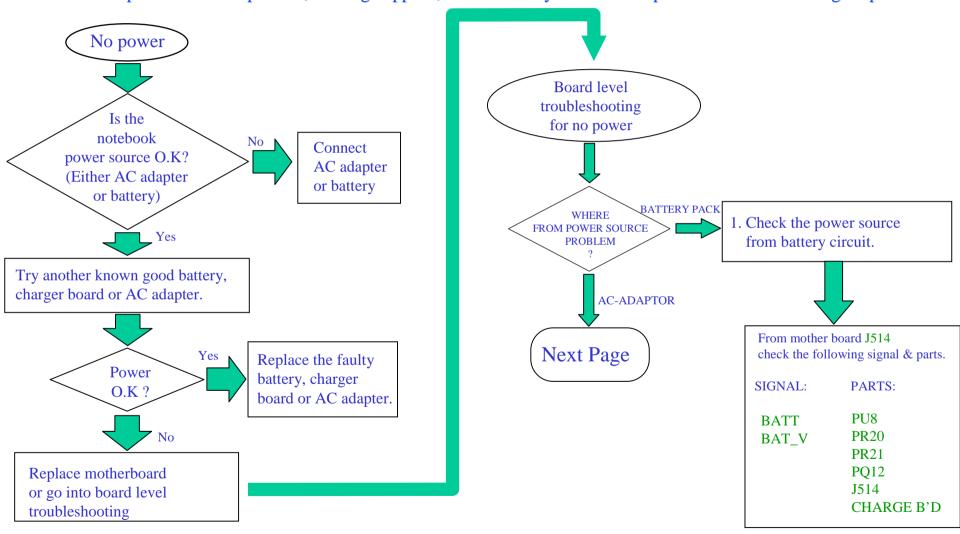

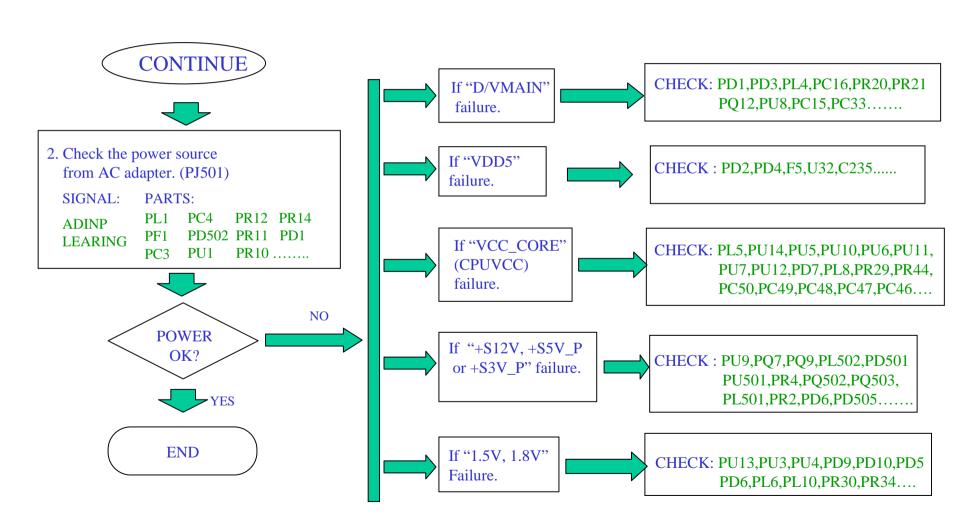

|-----------------------------------------------|-------------|

| 2. DEFINITION & LOCATION CONNECTORS/ SWITCHES | <b>P.40</b> |

| 3. DEFINITION & LOCATION MAJOR COMPONENTS     | <b>P.44</b> |

| 4. PIN DESCRIPTIONS OF MAJOR COMPONENTS       | <b>P.47</b> |

| 5. SYSTEM VIEW & DISASSEMBLY                  | <b>P.60</b> |

| 6. MAINTENANCE DIAGNOSTICS                    | P.84        |

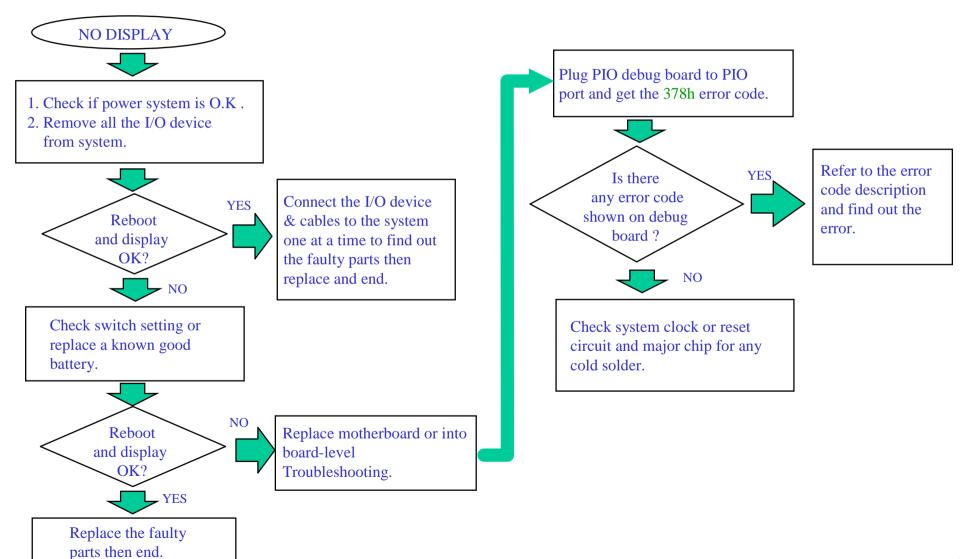

| 7. TROUBLE SHOOTING                           | P.88        |

| 8. SPARE PARTS LIST                           | P.120       |

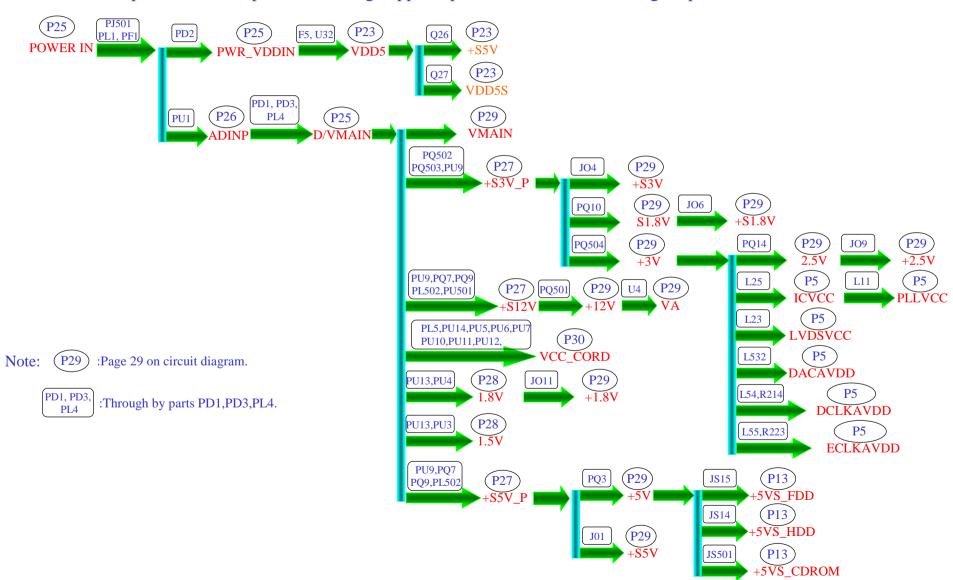

| 9. BLOCK DIAGRAM                              | P.128       |

| 10. EXPLODED DRAWING                          | P.129       |

| 11. CIRCUIT DIAGRAM.                          | P 130       |

### 1.1 HARDWARE ENGINEERING SPECIFICATION

### 1.1.1 General Description

This document describes the engineering specification for 7521 portable notebook computer system.

### 1.1.2 System Overview

The 7521 model motherboard will accept Intel Pentium III and Celeron processor with FC-PGA packaged. Which will supports the different levels of Pentium III CPU with FC-PGA package. Those are Pentium III 600/650/700/750/800 MHz, and Celeron 600/633/667/700/733 MHz.

This system is based on PCI architecture and is fully compatible with IBM PC/AT specification, which have standard hardware peripheral interface and support Intel Pentium III with FC-PGA package. The power management complies with Advanced Configuration and Power Interface (ACPI) 1.0. It also provides easy configuration through CMOS setup, which is built in system BIOS software and can be pop-up by pressing F2 at system start up or warm reset. System also provides icon LEDs to display system status, such as AC Power indicator, FDD, HDD, NUM LOCK, CAP LOCK, SCROLL LOCK, SUSPEND MODE and battery present, capacity & charging status. It also equipped with LAN, FIR, USB port, 3D stereo audio functions.

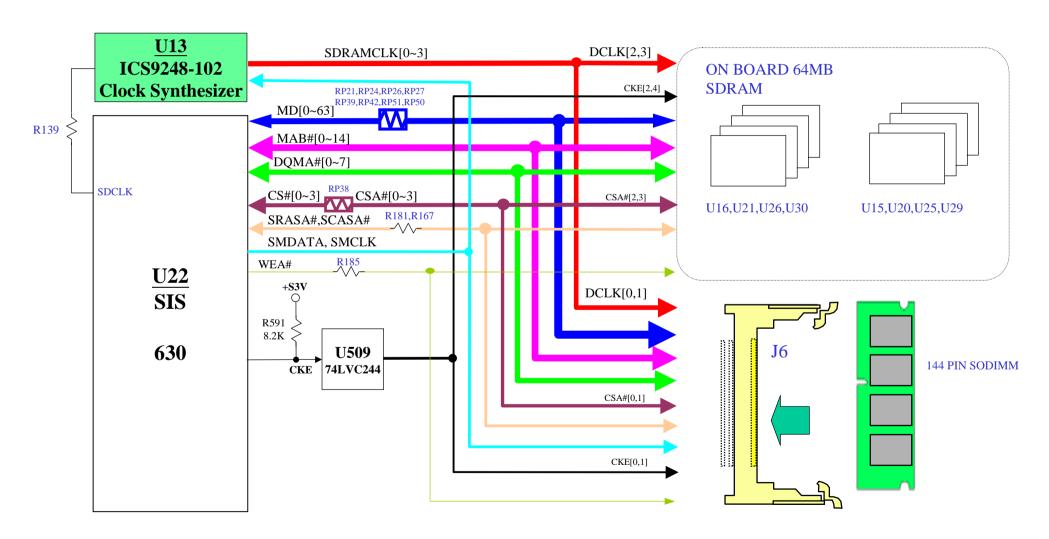

The memory subsystem supports 64MB on board SDRAM, one 144pin DIMM socket for upgrading up to 192 MB of DRAM using SDRAM DIMM module.

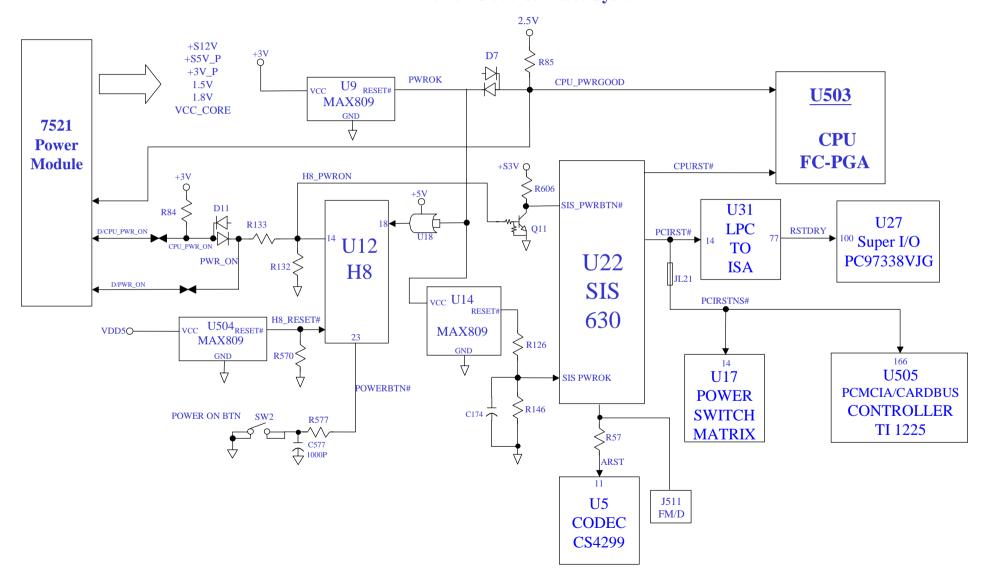

The SiS 630 integrates the north bridge chip, super south bridge and the real 128-bit 3D graphics accelerator all into one single chip. It provides 10/100M Fast Ethernet, 3D Positional Audio, Advance H/W DVD playback and 2D/3D graphics engine.

The TI 1225 cardbus controller supports PCMCIA and CARDBUS. The National Semiconductor PC97338 Super I/O controller integrates the standard PC I/O functions: floppy interface, two FIFO serial ports, one EPP/ECP capable parallel port, and support for an IrDA 1.1, 1.0 and sharp ASK compatible infrared interface. To provide for the increasing number of multimedia applications, an CODEC CS4299 is integrated onto the motherboard which support 16-bit stereo, Sound Blaster Pro, Windows Sound System compatibility, and full-duplex capabilities to meet the demands of interactive multimedia applications

A full set of software drivers and utilities are available to allow advanced operating systems such as Windows 95 or Windows 98 to take full advantage of the hardware capabilities. Features such as bus mastering IDE, Windows 95-ready Plug and Play, Advanced Power Management (APM) with application restart, software-controlled power shutdown..

### 1.2 Hardware System

### 1.2.1 System parts

- Central Processing Unite: using Intel Pentium III or Celeron microprocessors in FC-PGA packaged.

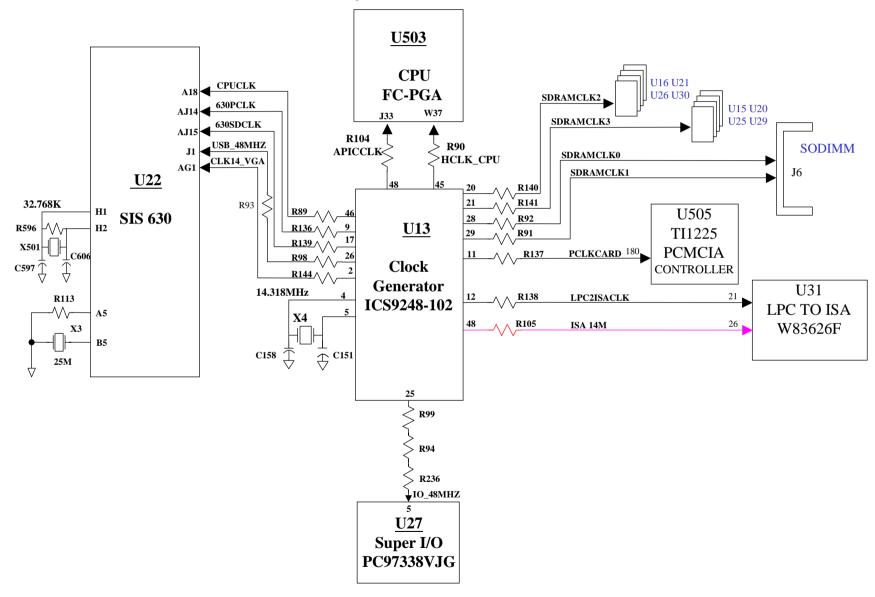

- Synthesizer: ICS9248-102.

- SiS 630: CPU/ PCI and CPU/AGP bridge with memory controller/LAN/IDE/USB/PMU controller.

- Super I/O Controller: NS PC 97338VJG.

- PCMCIA Interface Controller: TI 1225.

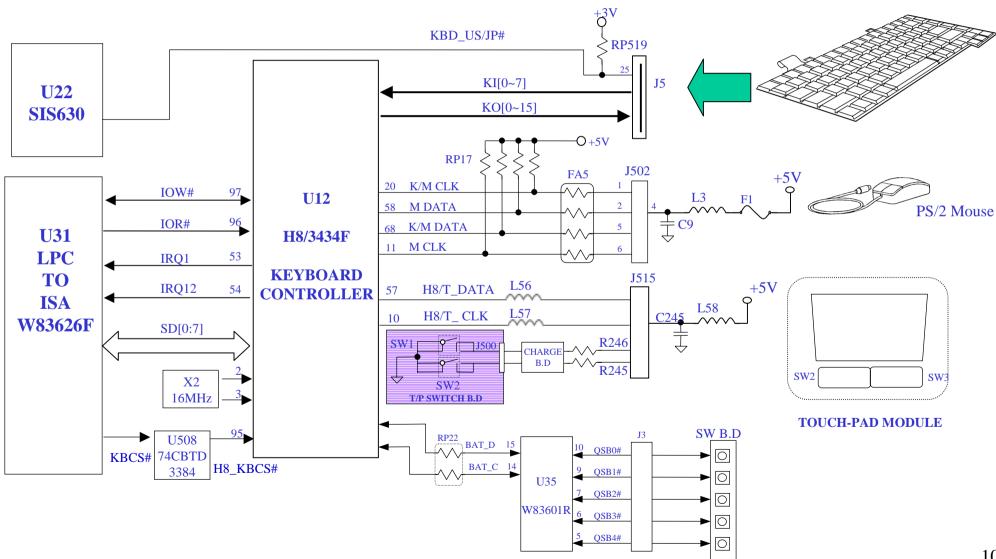

- Keyboard System: Hitachi H8 (3434F) universal keyboard controller.

- 3D Audio System: CRYSTAL CS 4299 CODEC.

- FIR port: HP HSDL-3600#007 FIR module.

- FAX/ MODEM: ASKEY 56Kbps Fax MODEM, software Modem (Option).

#### 1.2.2 CPU MODULE

- Intel Pentium III / Celeron Processors with 370 pins PGA package.

- Pentium Ⅲ 600/650/700/750/800 MHz, FC-PGA package at FSB 100MHz.

- Celeron 600/633/667/700/733 MHz, FC-PGA package.

### 1.2.3 Synthesizer

- System frequency synthesizer : ICS9248-102

- Maximized EMI suppression using Integrate Circuit System's spread spectrum technology.

- Three copies of CPU output, output to output skew between them within 175ps and seven copies of PCI output, output to output skew between them 500ps, fourteen copies of SDRAM output, output to output skew between them within 250ps.

- One 48MHz outout for USB and selectable 24/48 MHz output (pin25).

- Two buffer copies of 14.318MHz input reference signal.

- Supports up to 166MHz CPU or SDRAM operation.

- Supports two SDRAM DIMMS.

- Ideal for high performance Desktop/ Notebook designed using SIS630 chip set.

- I<sup>2</sup>C serial configuration interface.

### 1.2.4 SiS630 Slot 1/Socket 370 2D/3D Ultra-AGP<sup>TM</sup> Single Chipset

The single chipset SiS630, provide a high performance/ low cost Desktop soloution for the Intel Slot 1 and socket 370 series CPUs based system by integrated a high performance North Bridge, advanced hardware 2D/3D GUI engine and Super-South bridge. In addition. SiS630 provides system-on-chip solution that complies with Easy PC Initiative which supports instantly Available OnNow PC technology, USB, Legacy Removal and Slotless Design and FlexATX form factor.

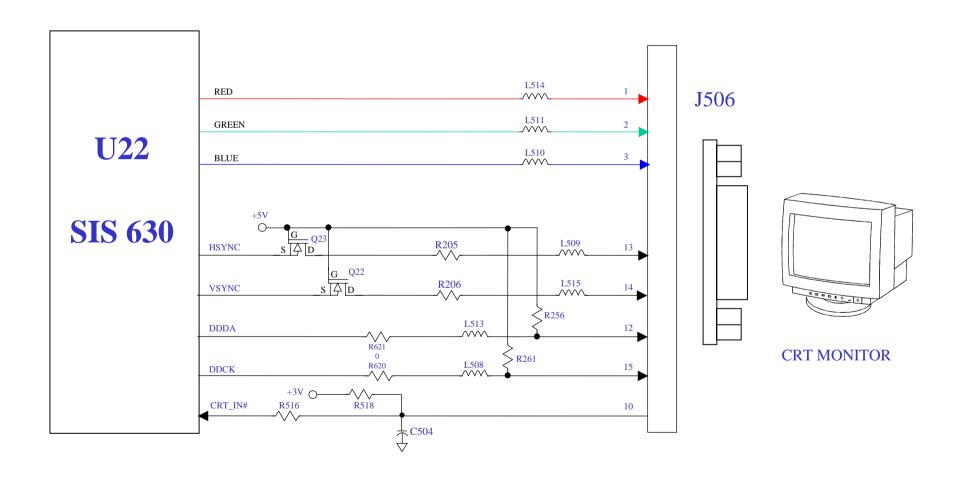

By integrating the UltraAGP<sup>TM</sup> technology and advanced 128-bit graphic display interface, SiS630 delivers AGP 4x-like performance and up to 2 GB/s memory bandwidth. Furthermore, SiS630 provides powerful hardware decoding DVD accelerator to improve the DVD playback performance. In addition to providing the standard interface for CRT monitors, SiS630 also

provides the Digital Flat Panel Port (DFP) for a standard interface between a personal computer and a digital flat panel monitor. To extend functionality and flexibility, SiS also provides the ?Video Bridge?(SiS301) to support the NTSC/PAL Video Output, Digital LCD Monitor and Secondary CRT Monitor, which reduces the external Panel Link transmitter and TV-Out encoder

for cost effected solution. SiS630 also adopts Share System Memory Architecture which can flexibly utilize the frame buffer size up to 64MB.

The "Super-South Bridge" in SiS630 integrates peripheral controllers / accelerators / interfaces. SiS630 provides a total communication solution including 10/100Mb Fast Ethernet for Office requirement and 1Mb HomePNA for Home Networking. SiS630 offers AC'97 compliant interface that comprises digital audio engine with 3D-hardware accelerator, on-chip

sample rate converter, and professional wavetable along with separate modem DMA controller. SiS630 also provides interface to Low Pin Count (LPC) operating at 33 MHz clock which is the same as PCI clock on the host, and dual USB host controller with five USB ports that deliver better connectivity and 2 x 12Mb bandwidth.

The built-in fast PCI IDE controller supports the ATA PIO/DMA, and the Ultra DMA33/66 function that supports the data transfer rate up to 66 MB/s. It provides the separate data path for two IDE channels that can eminently improve the performance under the multi-tasking environment.

#### **Features**

#### **Host Interface Controller**

- Supports Intel Pentium III/Celeron CPU at 100/66MHz Front Side Bus Frequency

- Synchronous Host/DRAM Clock Scheme

- Asynchronous Host/Dram Clock Scheme

#### **Integrated DRAM Controller**

- 3-DIMM/6-Bank of 3.3V SDRAM

- Supports NEC Virtual Channel Memory (VC-SDRAM) Technology

- Supports Memory Bus up to 133MHz

- System Memory Size up to 1.5GB

- Up to 512 MB per Row

- Supports 16Mb, 64Mb, 128Mb, 256Mb, 512Mb, SDRAM Technology

- Suspend-to-RAM (STR)

- Relocatable System Management Memory Region

- Programmable Buffer Strength for CS#, DQM[7:0], WE#, RAS#, CAS#, CKE, MA[14:0] and MD[63:0]

- Shadow RAM Size from 640KB to 1MB in 16KB incrementss

- Two Programmable PCI Hole Areas

#### Integrated A.G.P. Compliant Target /66Mhz Host-to-PCI Bridge

- AGP v2.0 Compliant

- Supports Graphic Window Size from 4MBytes to 256MBytes

- Supports Pipelined Process in CPU-to Integrated 3D A.G.P. VGA Access

- Supports 8 Way, 16 Entries Page Table Cache for GART to Enhance Integrated A.G.P. VGA Controller Read/Write Performance

- Supports PCI-to-PCI Bridge Function for Memory Write from 33MHz PCI Bus to Integrated A.G.P. VGA

### Meet PC99 Requirements PCI 2.2 Specification Compliant High Performance PCI Arbiter

- Supports up o 4 PCI Masters

- Rotating Priority Arbitration Scheme

- Advanced Arbitration Scheme Minimizing Arbitration Overhead

- Guaranteed Minimum Access Time for CPU and PCI Masters

#### **Integrated Host-to-PCI Bridge**

- Zero Wait State Burst Cycles

- CPU-to-PCI Pipeline Access

- 256B to 4KB PCI Burst Length for PCI Masters

- PCI Master Initiated Graphical Texture Write Cycles Re-mapping

- Reassembles PCI Burst Data Size into Optimized Block Size

#### **Fast PCI IDE Master/Slave Controller**

- Supports PCI Bus Mastering

- Native Mode and Compatibility Mode

- PIO Mode 0,1,2,3,4

- Multiword DMA Mode 0,1,2

- Ultra DMA 33/66

- Two Independent IDE Channels Each with 16 DW FIFO

#### **Virtual PCI-to-PCI Bridge**

#### **Integrated Ultra AGP VGA for Hardware 2D/3D Video/Graphics Accelerators**

- Supports Tightly Coupled 64 Bits 100mhz Host Interface to VGA to Speed Up GUI Performance and Video Playback

Frame Rate

- AGP v. 2.0 Compliant

- Zero-Wait-State 128x4 Post-Write Buffer with Write Combine Capability

- Zero-Wait-State 128x4 2-Way Read Ahead Cache Capability

- Re-locatable Memory-Mapped and I/O Address Decoding

- Flexible Design Shared Frame Buffer architecture for Display Memory

- Shared System Memory Area up to 64MB

- Built-in 8K Bytes Texture Cache

- 32-Bit VLIW Floating-Point Primitive Setup Engine

- Peak Polygon Rate: 4M Polygon/Sec@1 Pixel/Polygon With 16bpp, Bilinear Textured, Z Buffered and Alpha Blended

- Supports Flat and Ground Shading

- Supports High Quality Dithering

- Supports Z-Test, Stencil Test, Alpha Test and Scissors Clipping Test

- Supports Z Pre-Test for Reducing texture Read Dram Bandwidth

- Supports 256 Rops

- Supports Individual Z-Buffer and Render Buffer at the same time

- Supports 16/24/32 BPP Z Buffer Integrater/Floating Formats

- Supports 16/32 BPP Render Buffer Foramt

- Supports 1/2/4/8 Stencil Format

- Supports Per-Pixel Texture/Fog Perspective Correction

- Supports MIPMAP with Point-Sampled, Linear, Bi-Linear and Tri-Linear Texture Filtering

- Supports Single Pass Two MIPMAP Texture, One Texture on Clock

- Supports up to 2048x2048 Texture Size

- Supports 2?s Power of Width and height structure rectangular texture

- Supports 1/2/4/8 BPP Palletize Texture with 32 Bit ARGB Format

- Supports Fogging and Alpha Blending

- Supports Hardware Back Face Culling

- Supports YUV-to-RGB Color Space Conversion

- Supports CD/DVD to TV Playback Mode

- Supports DVD Sub-Picture Playback Overlay

- Built-in Programmble 24-bits True-Color RAMDAC up to 270 MHz Pixel Clock RAMDAC Snoop Function

- Supports VESA Standard Super High Resolution Graphic Modes

- 640x480 16/256/32K/64K/16M colors 120 Hz NI

- 800x600 16/256/32K/64K/16M colors 120 Hz NI

- 1024x768 256/32K/64K/16M colors 120Hz NI

- 1280x1024 256/32K/64K/16M colors 120Hz NI

- 1600x1200 256/32K/64K/16M colors 100Hz NI

- 1920x1200 256/32K/64K/16M colors 80Hz NI

- Cooperate with iS Video Bridge ?to support

- NTSC/PAL Video Output

- Digital LCD Monitor

- Secondary CRT Monitor

#### **Low Pin Count Interface**

- Forwards PCI I/O and Memory Cycles into LPC bus

- Translates 8/16 bit DMA cycles into PCI bus cycles

#### Advanced PCI H/W Audio & Modem

- Advanced Wavetable Synthesizer

- DirectSound<sup>TM</sup> 3D

- Advanced Streaming Architecture

- High Quality Audio and AC"97/98 Support

- Full Legacy Compatibility

- Telephony & Modem

- Software support

- Meets ACPI 1.0 Requirement

- Meets APM 1.2 Requirement

- ACPI Sleep States Include S1, S2, S3, S4, S5

- CPU Power States Include C0, C1, C2, C3

- Power Button with Override

- RTC Day-of-Month, Month-of-Year Alarm

- LED Blinking in S0, S1, S2, S3

- PCI Bus Power Management Interface Spec. 1.0

#### **Integrated DMA Controller**

- Two 8237A Compatible DMA Controller

- 8/16 bit DMA data transfer

- Distributed DMA Support

#### **Integrated Interrupt Controller**

- Two 8237A Compatible DMA Controller

- Two 8259A Compatible Interrupt Controllers

- Level or Edge Triggered programmable

- Serial IRQ

- Interrupt Source Re-routable to Any IRQ channel

### Three 8254 Compatible Programmable 16-bits counters

- System timer interrupt

- Generate refresh request

- Speaker output

### **Integrated Keyboard Controller**

- Supports PS/2 mouse interface

- Password security and password power-up

- System sleep and power-up by Hot-Key

- KBC and PS2 mouse can be individually disabled

#### **Integrated Real Time Clock (RTC) with 256B CMOS SRAM**

- Supports ACPI Day-Month and Month-of-Year- Alarm

- 256 Bytes of CMOS SRAM

- Provides RTC H/W Year 2000 Solution

#### **Universal Serial Bus Host Controller**

- Open HCI Host Controller with Root Hub

- Two USB Host Controller

- Five USB Ports

- Supports Legacy Devices

- Over Current Detection

#### I<sup>2</sup>C Bus/SMBus Series Interface

- Plug and Play Compatible

- High-Performance 32-Bit PCI Bus Master Architecture with Integrated Direct Memory

- Access (DMA) Controller for Low CPU and Bus utilization

- Supports PCI Device ID, Vendor ID / Subsystem ID, Subsystem Vendor ID

- Programming through the EEPROM interface

- Implements Optional PCI 3.3v Auxiliary Power Source 3.3Vaux Pin and Optional PCI

- IEEE 802.3 and 802.3u Standard Compatible

- IEEE 802.3u Auto Negotiation and Parallel Detection for Automatic Speed Selection

- Full Duplex and Half Duplex Mode for both 10 and 100 Mbps

- Fully Compliant Ansi X3.263 Tp-Pmd Physical Sub-Layer which includes adaptive

- Single 25mhz Clock for 10 and 100 Mbps Operation

- Power Down of 10 base-T/100base-Tx sections when not in use

- Supports 10base-Tx, 100base-Tx

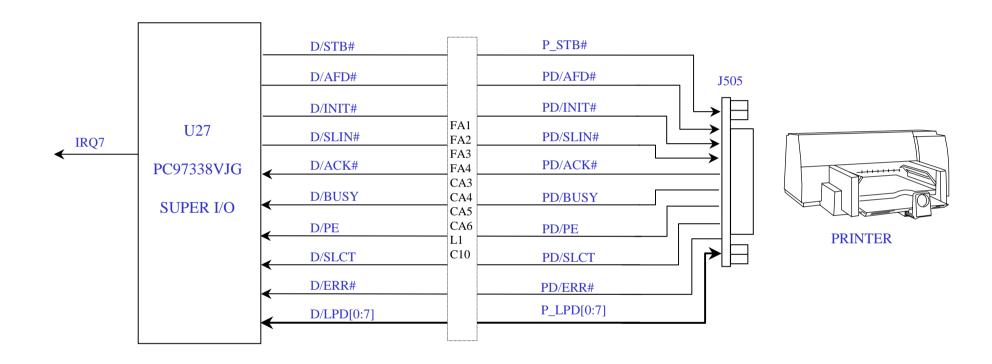

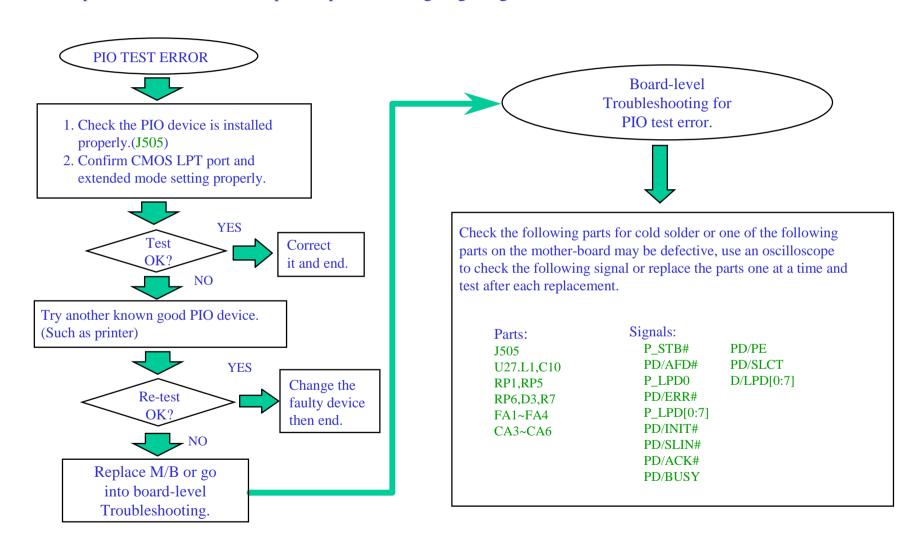

### 1.2.5 Super IO: NS PC 97338VJG

- High speed PC16550A compatible UART with receive/transmit 16 Bytes FIFO programmable serial baud rate generator

- Multi-mode parallel port support including standard port, EPP/ECP (IEEE1284 compliant, 2 interrupt pins)

- Plug and Play module

- FDC, 100% IBM compatible, S/W & register compatible to 82077 with 16Bytes data FIFO Support 3-Mode FDD

- FIR/MIR/SIR/SHARP ASK for Infrared application.

- COM2

■ IrDA 1.0 / IrDA 1.1 / SHARP ASK

- Baud rate: max. 4Mb

- Link distance: 0.01 to 1 m

- Half angle:  $\pm 15... \rangle$  .Bit Error Rate (BER) : 10  $^{\text{-9}}$

- Peak wavelength: 0.85 - 0.90 mm.

■ TQFP 100 pins

■ Standby mode: control by software

Default configuration:

|                                       | IO address | IRQx | DRQx |

|---------------------------------------|------------|------|------|

| COM1                                  | 3F8-3FF    | 4    | -    |

| FIR/MIR/SIR/<br>SHARP ASK<br>( COM2 ) | 278-27F    | 3    | -    |

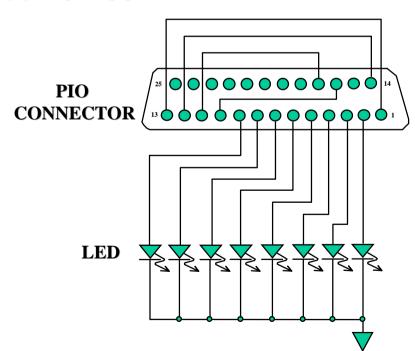

| PIO                                   | 378-37F    | 7    | -    |

| FDD                                   | 3F0-3FF    | 6    | 2    |

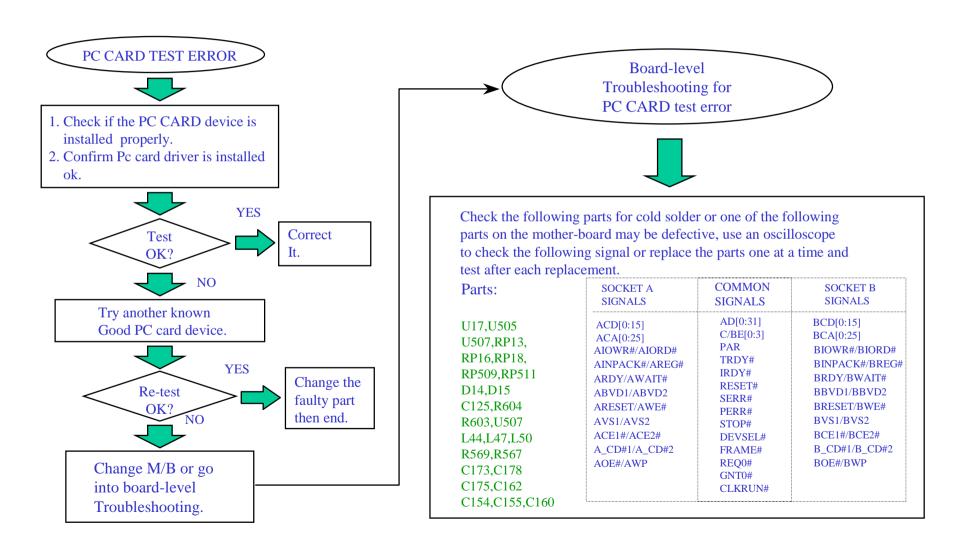

### 1.2.6 PC CARD interface controller: TI1225

- ACPI 1.0 Compliance

- PCI Power Management interface specification 1.0 Compliance

- Supports distributed DMA (DDMA) and PC/PCI DMA

- Advanced submicron, low-power CMOS technology.

- Supports two I/O windows and two memory windows available to each cardbus socket.

- Supports five PCI memory windows and two I/O windows available to each PC CARD16 socket.

- Supports Burst Transfers To Maximize Data Throughput On Both PCI Buses

- Provides Serial Interface To TI TPS2202/TPS2206 Dual Slot PC CARD Power Interface Switch

- Supports up to 5 general purpose I/O

- Multi-Function PCI Device With Separate Configuration Space For Each Socket

- Pipelined architecture allows greater than 130Mbps second throughput from cardbus to PCI and from PCI to cardbus.

- Support PCI Bus Lock (/LOCK)

- 3.3-V core logic with universal PCI interface

- PCI Local Bus Specification Revision 2.1 compliant

- Fully compatible with the Intel 430TX(Mobile Triton II) chipset

- 1995 PC Card Standard compliant

- Supports two 16-bit PC card or Cardbus card; sockets powered at 3.3V or 5V with hot insertion and removal

- Provides a serial EEPROM interface for loading the subsystem ID and subsystem vendor ID.

- ExCA compatible Registers mapped in memory or I/O space.

- Supports ring indicate output, SUSPEND#, and programmable output select for CLKRUN#.

- Provides socket activity LED signals.

- Provides zoom video support signals.

- Provides zoom video port function in socket B.

- 208-Pin LQFP package

### 1.2.7 DUAL-SLOT PC CARD POWER INTERFACE SWITCH: TPS2206

- Fully Integrated Vcc and Vpp Switching for Dual-Slot PC Card Interface

- P 2 C3-Lead Serial Interface Compatible With CardBus Controllers

- 3.3 V Low-Voltage Mode

- Meets PC Card Standards

- RESET for System Initialization of PC Cards

- 12-V Supply Can Be Disabled Except During 12-V Flash Programming

- Short Circuit and Thermal Protection

- 30-Pin SSOP (DB) and 32-Pin TSSOP (DAP)

- Compatible With 3.3-V, 5-V and 12-V PC Cards

- Lower DS(on) (140-m .5-V Vcc Switch; 110-m .3.3-V Vcc Switch)

- Break-Before-Make Switching

### 1.2.8 Keyboard system: H8(3434F) universal keyboard controller

- CPU

- Two-way general register configuration

- Eight 16-bit registers or Sixteen 8-bit registers

- High-speed operation

- Maximum clock rate: 16Mhz at 5V

- Memory

- Include 32KB ROM and 1KB RAM

- 16-bit free-running timer

- One 16-bit free-running counter

- Two output-compare lines

- Four input capture lines

- 8-bit timer (2 channels)

- Each channel has one 8-bit up-counter, two time constant registers

- PWM timer (2 channels)

- Resolution: 1/250

- Duty cycle can be set from 0 to 100%

- I<sup>2</sup>C bus interface (one channel)

- Include single master mode and slave mode

- Host interface (HIF)

- 8-bit host interface port

- Three host interrupt requests (HIRQ1,11,12)

- Regular and fast A20 gate output

- Keyboard controller

- Controls a matrix-scan keyboard by providing a keyboard scan function with wake-up

- Interrupts and sense ports

- A/D converter

- 10-bit resolution

- 8 channels : single or scan mode (selectable )

- D/A converter

- 8-bit resolution

- 2 channels

- Interrupts

- nine external interrupt lines : NMI# , IRQ0 to 7#

- 26 on-chip interrupt sources

- Power-down modes

- Sleep mode

- Software standby mode

- Hardware standby mode

- A single chip microcomputer

- On-chip flash memory

- Maximum 64-kbyte address space

- Support three PS/2 port for external keyboard ,mouse and internal track pad.

- Support SMI,SCI trigger input:

- Cover switch

- Battery charging control

- Smart Battery monitoring

- Control D/D system on/off

- Fan control and LED indicator serial interface

- 100pin TQFP

### 1.2.9 Memory System

### **1.2.9.1 Main Memory**

- HYUNDAI: GM72V281641AT-7K SDRAM

- NEC: UPD45128163G5-A80-9JF SDRAM

- one chip memory size: 4Banksx1Mx16bit SDRAM.

- Standard 54 pin TSOP-II package.

- Power supply:  $3 \pm 0.3V$

- Supports One JEDEC 144-pin S.O. DIMM sockets on Mother Board for expansion

- Supports 3.3V SDRAM

- 2 banks on one socket.

- SDRAM accesses time from clock: 6ns

- Memory bus bandwidth: 64 bits

■7521 Supports 64 MB SDRAM on board and one 144pin DIMM socket for upgrading up to 320MB of DRAM.

Here are some main memory system essential characteristics:

- One chip 4Banksx1Mx16bit on board 64 MB

- 144-pin S.O. DIMM socket

- Memory Voltage  $3.3V \pm 10\%$

- Banks on DIMM Total:2

- Mixed type DRAM Only supports SDRAM

### 1.2.10 Interface

- Power Supply Jack.

- One Standard Parallel Port With ECP/EPP Functions

- Supports Two USB port for all USB device.

- Supports Macrovision's TV-OUT connector.(layout only)

- Tunable volume by variable resistor.

- Two Serial Ports, One For COM1/COM2, The Other For FIR/MIR/SIR/SHARP ASK

- One External CRT Connector For CRT Display

- One PS/2 Interface For External KB, Mouse Or Other Devices

- Two Cardbus Sockets

- Cable For Connection Between M/B And Panel.

- Cable For Connection Between M/B And Backlight BD.

- Headphone Out Jack, Microphone Input Jack And Line In Jack.

- One MODEM RJ-11 phone jack for PSTN line and RJ-45 for LAN.

- Battery translation board connection between M/B and battery.

- Quick start buttons translation board (QSB) connection between M/B and five Buttons.

- Internet quick start button translation board (IQSB) connection between M/B and touch pad, five LEDs, two Buttons.

- FDD-HDD translation board connection between M/B and floppy, hard disk.

- One CD-ROM connector on M/B.

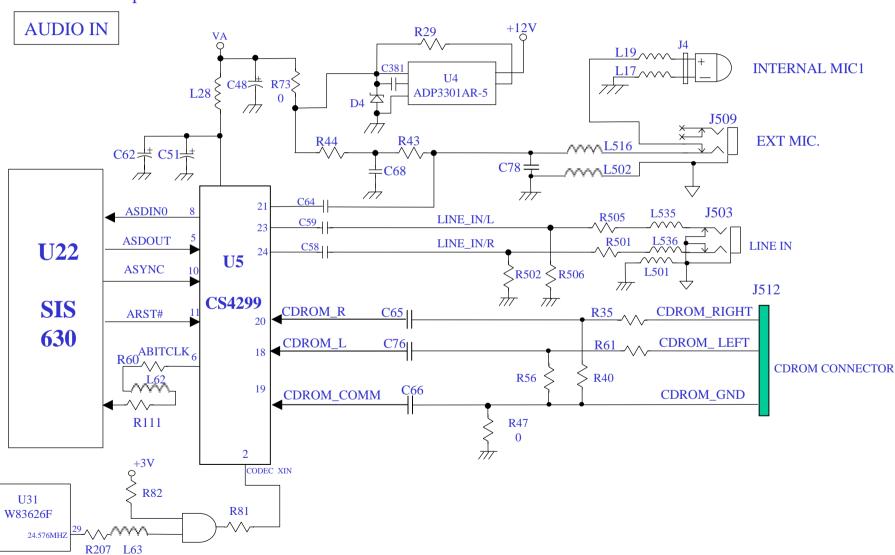

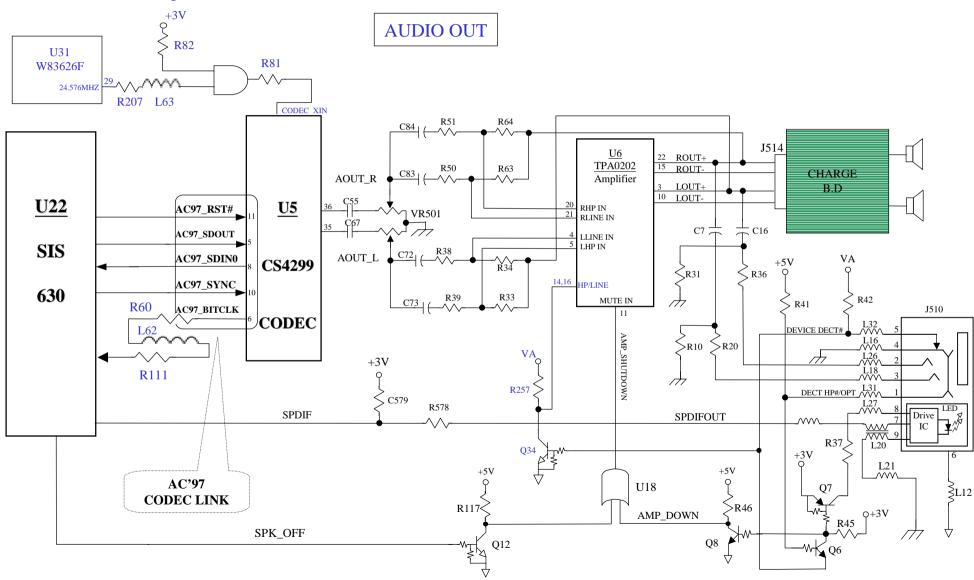

### 1.2.11 Audio System: AC'97 CODEC CS4299

- AC'97 CODEC CS4299 provides a complete high quality audio solution, Feature Include:

- MPU-401 interface

- FM synthesizer

- Game Port

- MIDI port.

- MODEM

- CD-ROM

- User-Defined GPIO

- Volume Control: Rotary VR

- Stereo BTL 2x1 W Amplifiers(TPA0202) With 8 Ohm Load.

- CD-ROM IDE Interface

- 18-bit Stereo ADC & 20-bit Stereo DAC For Record And Play Back

- Programmable Sample Rates From 20Hz To 20kHz For Record And Playback

- Microphone in \* 1 (3.5 mm phone-jack)

- Headphone out \* 1: stereo (3.5 mm phone-jack and SCMS support)

- Line in \* 1(3.5 mm phone-jack)

- Built-in Speaker \* 2 (1w, 8 ohm)

- Built-in Microphone \* 1

- Note: For Those Input Source Not Using Should Be Set Mute In Order To Reduce Noise. Like Line In

### 1.2.12 IR MODULE: HSDL-3600#007

- Fully Compliant to IrDA 1.1 Specifications

- 115.2 kb/s to 4 Mb/s operation

- excellent nose-to-nose operation

- Compatible with ASK, HP-SIR, and TV Remote

- IEC825-Class 1 Eye Safe

- Wide Operating Voltage Range

- 2.7 V to 5.25 V

- Small Module Size

- 4.0 x 12.2 x 5.1 mm (HxWxD)

- Complete Shutdown

- TXD, RXD, PIN diode

- Low Shutdown Current

- 10 nA typical

- Adjustable Optical Power Management

- Adjustable LED drive-current to maintain link integrity

- Single Rx Data Output

- FIR Select pin switch to FIR

- Integrated EMI Shield

- Excellent noise immunity

- Edge Detection Input

- Prevents the LED from long turn-on time

- Interface to various Super I/O and Controller Devices

- Designed to Accommodate Light Loss with Cosmetic Window

- Minimum External Components Required

## **1.2.13 Special Feature Function**

### 1.2.13.1 Hot Key Function

| Keys Combination | Feature                | Meaning                                          |

|------------------|------------------------|--------------------------------------------------|

| Fn + F5          | LCD/external CRT       | Rotate display mode in LCD only, CRT only and    |

|                  | switching              | simultaneously display.                          |

| Fn + F6          | Brightness down        | Decreases the LCD brightness / No function in    |

|                  |                        | DSTN model                                       |

| Fn + F7          | Brightness up          | Increases the LCD brightness / No function in    |

|                  |                        | DSTN model                                       |

| Fn + F10         | Enable/Disable Battery | Toggle Battery Warning on/off                    |

|                  | Warning Beep           |                                                  |

| Fn + F11         | Panel Off/On           | Toggle Panel Off/On                              |

| Fn + F12         | Suspend to DRAM/HDD    | Force the computer into either Suspend to HDD or |

|                  |                        | Suspend to DRAM mode depending on BIOS           |

|                  |                        | Setup.                                           |

### 1.2.13.2 Quick Start Button function

| Keys | Feature                                                  | Meaning                           |

|------|----------------------------------------------------------|-----------------------------------|

| IQSB | Mail Received Button (or function "Recognizable Signal") | Determined by Software component. |

| ESB1 | Entertainment Quick Key                                  | Determined by Software component. |

| ESB2 | Instant Internet                                         | Determined by Software component. |

| ESB3 | My Presario                                              | Determined by Software component. |

| ESB4 | Search                                                   | Determined by Software component. |

| ESB5 | Email                                                    | Determined by Software component. |

### **1.2.13.3 Flash ROM (BIOS)**

7521 system utilizes the state-of-the-art Flash EEPROM technology. User can upgrade the system BIOS in the future just running the program from MiTAC.

#### 1.2.13.4 LED Indicators

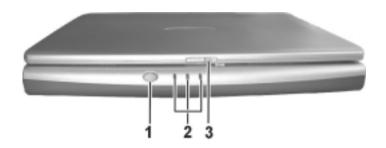

System has ten status LED indicators to display system activity which include above keyboard and below touch pad:

1. Four LED indicators below touch pad:

From left to right that indicates MAIL RECEIVED, AC POWER, BATTERY POWER and BATTERY STATUS:

- Mail Received status: This LED lights to indicate that User received E-mail status. User can define color of LED (yellow or green) to indicate relation of transmitter.

- AC POWER: This LED lights green when the notebook is being powered by AC, and flash (on 1 second, off 1 second) when Suspend to DRAM is active using AC power. The LED is off when the notebook is off or powered by batteries, or when Suspend to Disk.

- BATTERY POWER: This LED lights green when the notebook is being powered by batteries, and flashes (on 1 second, off 1 second) when Suspend to DRAM is active using battery power. The LED is off when the notebook is off or powered by AC, or when Suspend to Disk.

- BATTERY STATUS: During normal operation, this LED stays off as long as the battery is charged. When the battery charge drops to 10% of capacity, the LED lights red, flashes per 1 second and beeps per 2 second. When AC is connected, this indicator glows green if the battery pack is fully charged, or orange (amber) if the battery is being charged.

- 2. Six LED indicators above keyboard:

From left to right that indicates CD-ROM/MO, HARD DISK DRIVE, FLOPPY DISK DRIVE, NUM LOCK, CAPS LOCK and SCROLL LOCK.

### 1.2.13.5 COM port assignment

■ COM1: MODEM / RS-232 / Disable

■ COM2: IR / RS-232 / Disable

### 1.3 SMM and System BIOS

### 1.3.1 System Management Mode

7521 system has built in several power saving modes to prolong the battery usage for mobile purpose. User can enable and configure different degrees of power management modes via ROM CMOS setup (booting by pressing F2 key). Following are the descriptions of the SMM and power management modes supported.

#### **1.3.1.1 Full On Mode**

In this mode, each device is running with the maximal speed. CPU clock is up to its maximum.

#### **1.3.1.2 Doze Mode**

In this mode, CPU will be toggling between on & stop grant mode either. The technology is clock throttling. This can save battery power without loosing much computing capability. The CPU power consumption and temperature is lowered in this mode.

### 1.3.1.3 Standby Mode

For more power saving, it turns of f the peripheral component. In this mode, the following is the status of each device.

■ CPU: Stop grant

LCD: backlight off

HDD: spin down

FDD: standby

### 1.3.1.4 Suspend Mode

The most chipset of the system is entering power down mode for more power saving. In this mode, the following is the status of each device.

### **1.3.1.4.1 Suspend to DRAM:**

■ CPU: off

■ SiS630: Partial off

■ VGA: off

■ PCMCIA: off

■ Super IO: off

■ Audio: off

■ SDRAM: Self Refresh.

#### **1.3.1.4.2** Suspend to HDD:

- All devices are stopped clock and power-down,

- System status is saved in HDD.

- All system status will be restored when powered on again.

### 1.3.1.5 Other power management functions

#### 1.3.1.5.1 HDD & Video access

System has the ability to monitor video and hard disk activity. User can enable monitoring function for video and/or hard disk individually. When there is no video and/or hard disk activity, system will enter next PMU state depending on the application. When the VGA activity monitoring is enabled, the performance of the system will have some impact.

#### 1.3.1.5.2 Battery Warning

System also provides Battery capacity monitoring and gives user a warning so that users have chance to save his data before battery dead. Also, this function protects system from mal-function while battery capacity is low.

-Battery Warning: Capacity below 10%, Battery Capacity LED flashes per second, system beeps per 2 seconds. (System beeps only if BIOS setup enable Battery Warning Beeping.) System will Suspend to HDD after 2 Minute if BIOS setup enable this function or system will runs until battery dead without any protection.

#### 1.3.1.5.3 Cover Switch

System automatically provides power saving on monitoring Cover Switch. It will save battery power and prolong the usage time when user closes the notebook cover unintentionally but the system still in power on mode. There are two functions to be chosen.

- 1. Switch to CRT

- 2. Panel Off

- 3. Suspend to DRAM or Suspend to Disk by CMOS setup

### 1.3.1.5.4 Battery Warning State

RedSea system provides battery management function and gives warning while battery is in Its low power state. When the battery capacity is below 10% (Battery Warning State), system will generate beep for every 2 seconds. When hearing the beeping, it is recommended that user should plug in AC adapter to get power from external source, or stop working and save his data file to prevent disaster results.

#### 1.3.1.5.5 Battery Low State

After Battery Warning State, and battery capacity is below 4%, system will generate beep for twice second.

#### 1.3.1.5.6 Battery Dead State

When the battery voltage level reaches 9 volts, system will shut down automatically in order to extend the battery packs' life.

### 1.3.2 System BIOS

### 1.3.3 Fan power on/off management

FAN is controlled by H8 embedded controller which using LM45 to sense CPU temperature and PWM to control fan speed.

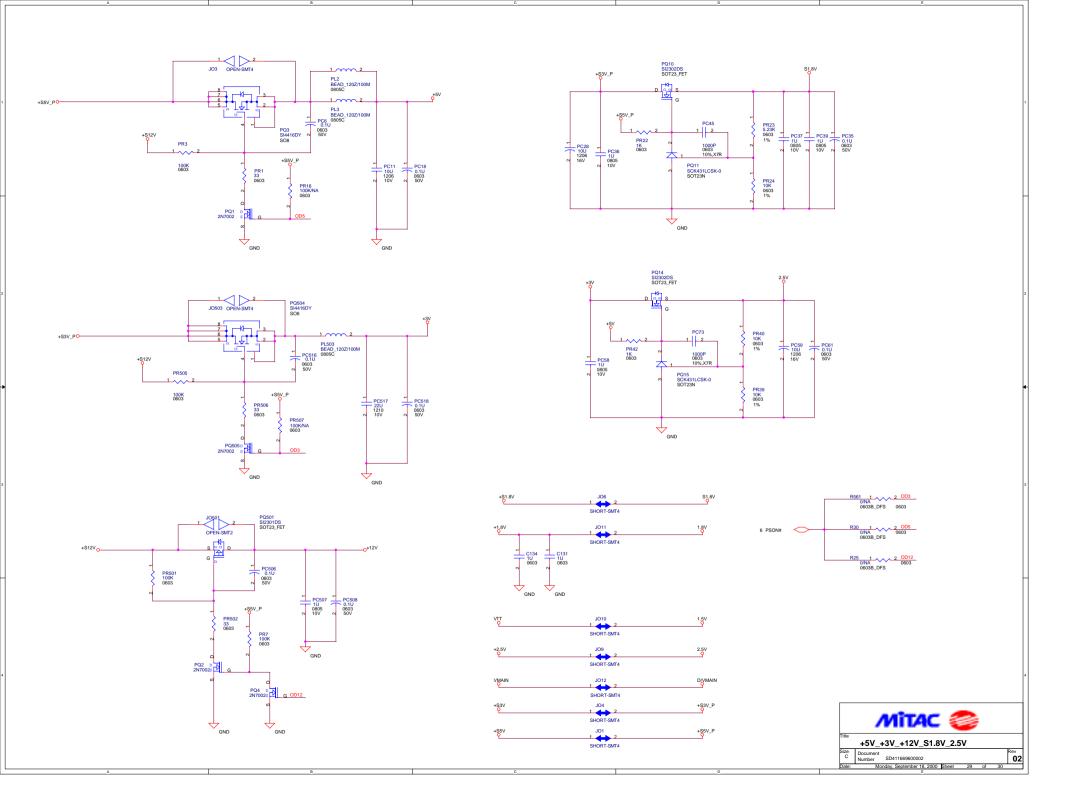

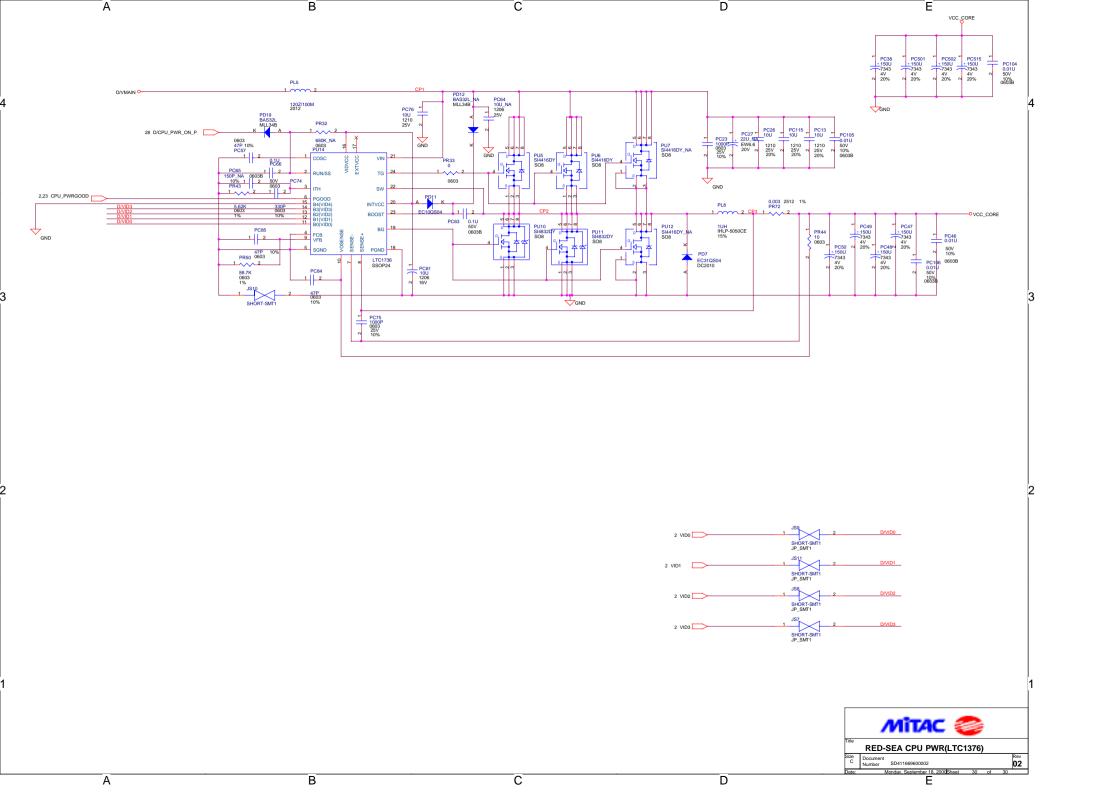

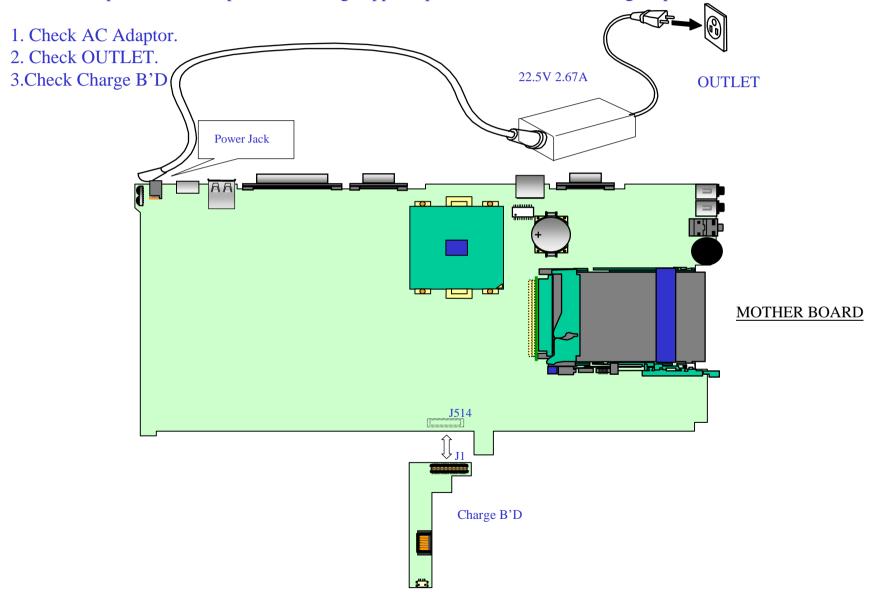

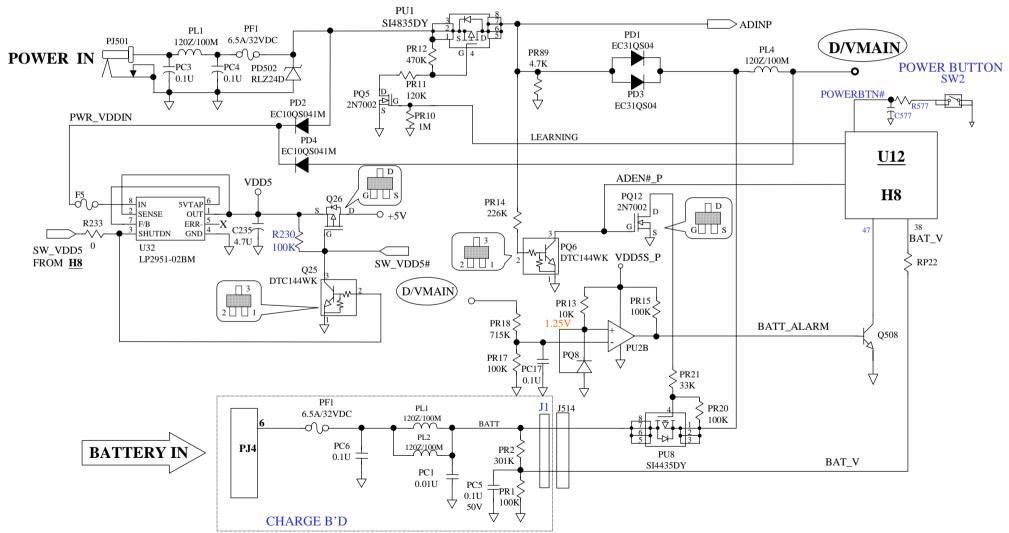

### 1.4 Power Supply System

■ Please refer to the document for 7521 adapter, DC-to-DC and backlight BD.

### 1.5 Peripheral Components

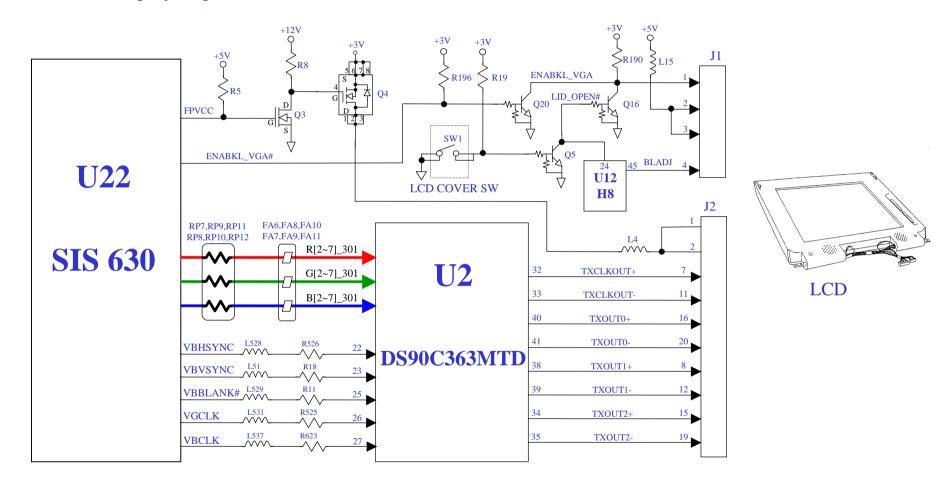

### **1.5.1 LCD PANEL**

- Hyundai 14X13

- 1024X768 XGA TFT Panel

- Display size (diagonal): 14.1 inch

- 262,144 colors display

- 1 channel LVDS Interface (Flat Link, Ti)

- Display Mode: Normal White

- Back-light unit : CCFL, 1 tube

- DC for Panel: 3.3V+-0.3V

- Pixel pitch : 0.279(H)X0.279(V)

- Power supply current : 320 mA (Typ)

- Lamp start Voltage: 1500Vrms (25 °C)

### 1.5.2 HDD

■ FUJITSU MHK2120AT : 12 GB Capacity

- 12.0GB Capacity

- Number of head: 3

- Number of cylinders: 14,784

- Bytes per sector: 512

- Recording method: 16/17 MTR

- Track density: 24,300 TPI

- Bit Density : 383 Kbpi

- Rotational Speed: 4,200 rpm +-1%

- Average Latency: 7.14 ms

- Interface : ATA-5 (Max. Cable length : 0.46 m)

- Data transfer rate :

- To/From Media: 12.5 to 22.3 MB/s

- To/From Host: 66.6 MB/s Max (Ultra-DMA mode 4)

- Data Buffer Size: 512 KB

- Spin up current : 0.9A<sub>rms</sub>

- Max. Power Consumption : 4.5W (During spin up)

- Physical Dimensions (H X W X D): 9.5 mm X 100.0 mm X 70.0 mm

- 15GB, 20GB, 24GB HDD To Be Defined.

### 1.5.3 Keyboard

■ External keyboard: Supports IBM 106 key compatible keyboard

- Key pitch: 19 mm

- Windows95 applied

■ Internal keyboard: Compatible Japanese keyboard layout (90 keys)

### 1.5.4 Floppy Disk Drive

■ Mitsumi D353G

■ Using High density (2HD) 3.5 inch disk

■ Data transfer rate: 500k bits/sec

■ Disk rotational speed: 300 rpm for 2mode, 360rpm for 3mode

■ Track density: 135 tpi

■ Track to Track time: 3msec

#### 1.5.5 Touch Pad

■ Logic Tech: 904255-0002

■ Vcc: 5V +- 0.5

■ Icc(max): 15 mA

■ Interface : PS/2

■ X/Y position resolution : 480+-50 CPI

■ Dimension: 66mm x 50mm x 5.0mm

• effective area: 55mm x 39 mm

■ Operating Temp. : 0 - 50 degree C

■ Storage Humidity: 5 - 90 %,

■ Storage Temp. : -20 - + 60 degree C

■ ESD: 15KV applied to front surface

### **1.5.6 24X CD-ROM Drive**

- System has optional MATSUSHITA UJDA150 24X speed CD-ROM drive, LGS CRN8241B 24X speed CD-ROM drive, or TEAC CD-224E-A92 24X speed CD-ROM drive.

- Hardware interface is compliant with ATAPI IDE specification.

- IDE second channel (170h). The default drive is D. User should install the CD-ROM device driver in order to operate this device. This CD-ROM drive also support audio interface. Co-operate with audio circuit, CD-ROM drive can work as a CD player.

- Ejection: Manual eject using the eject button/Automatically eject using the tray

- XM-1802B:

- average data transfer rate of 3,600 KB/s

- average random seek time of 100ms

- Random access time of 110ms.

- Small size (only 12.7(H) x 128(W) x 129(D)mm)

- Extremely low weight of 230g

- Low average power consumption of 2.4W (maximum only 3.2W).

### 1.5.7 DVD-ROM drive

MATSUSHITA: UJDA520L-SH 4X speed

- Fast 170 ms Random Access Time (DVD)

- Max. 4X (DVD)/Max. 24X (CD)

- Max. 5,408 Kbytes/s (DVD)/Max. 3,600 Kbytes/s (CD) Sustained Transfer Rate.

- PIO mode-4 ATAPI Drive (16.7 Mbyte/s)

- DMA: Multi word DMA transfer mode-2 (Transfer Rate 16.7 Mbyte/s)

- : Ultra DMA mode-2 (Transfer Rate 33.3 Mbyte/s)

### 1.5.8 CD-R/RW drive

- MATSUSHITA: UJDA310

- WRITE 4X-Speed

- READ max 20X-Speed (CD-RW max 14X-Speed)

- PIOMODE: 16.6MB/s; Mode 4

- DMAMODE: 4.2MB/s; Mode 0

- Write: 150KB/s (Normal speed), 300KB/s(2X speed), 600KB/s(4X speed)

- Buffer memory: 2MB

- Access speed 150ms (Typ.)

### 1.5.9 LED Indicators

- Lower ICON LEDs on M/B

- Mail Received status (**left** 1)

- AC POWER(Left 2)

- BATTERY POWER(right 2)

- BATTERY STATUS(right 1)

- Upper ICON LEDs on M/B

- CD-ROM/MO(left 1)

- HARD DISK DRIVE(left 2)

- FLOPPY DISK DRIVE(left 3)

- NUM LOCK(right 3)

- CAPS LOCK(right 2)

- SCROLL LOCK(**right** 1)

## **1.5.10 IR port**

- HP HSDL-3600#007 FIR Module

- Meet IrDA Physical Layer Specification

- 1 cm to 1 Meter Operating Distance

- 30 degree Viewing Angle

- Support Two Channels 2.4 Kb/s to 115.2Kb/s and 1.15Mb/s to 4.0 Mb/s

## 1.5.11 CMOS Battery

- CR2032 3V 220mAh lithium battery

- When AC in or system main battery in , CMOS battery will no power consumption.

- AC or main battery not exist, CMOS battery life at less (220mAh/5.8uA) 4 years.

- In normal condition, battery life is at less over 4 years. Battery was put in battery holder, can be replaced

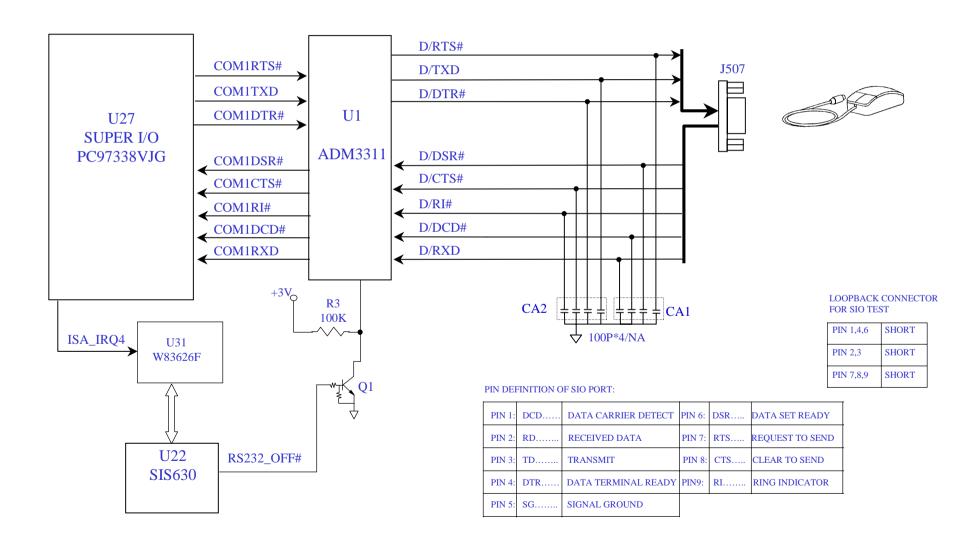

## 1.5.12 Serial Interface

- Using AD ADM3311ARU chip

- ESD rating:±3KV

- Lead TEMP.(Soldering 10sec):+300 °C

- Number of RS-232 drivers : 3

- Number of RS-232 receivers : 5

- 28 pin SSOP package

- Support shutdown mode(pin 23).

- -40  $^{\circ}$ C +85  $^{\circ}$ C Operating voltage range : 3V  $\pm 0.3$ V

- MAX. data rate:460 kbps

- Shutdown supply current : 15(TYP)uA- 50(MAX)Ua

## 1.5.13 PCMCIA socket

- Operating temperature range : -55  $^{\circ}$ C +85  $^{\circ}$ C

- Insertion force : 39.2N (MAX)

- 10000 times insertion and withdrawal at the cycle rate 400- 600cycles/hour and no

- evidence of breakage and cracks on the component.

- In +85  $^{\circ}$ C 250h life test conditions should be no evidence of breakage and

- Cracks on the component.

- In -55  $^{\circ}$ C 96h life test conditions should be no evidence of breakage and

- Cracks on the component.

## 1.5.14 FAN

- Dimension : Made by Sunonwealth Electric Machine Industry Co. Ltd.

- Model number: KD0502PEB2-8 DC brushless fan

- Operating speed: 8000 rpm.

- Input voltage : 5V

- Operating temperature : -10 +70 degree C.

- Weight: 7g

- Direction of rotation : C.C.W.

- Noise level : 27 dB(A)

- Rated power: 0.6 W

- Static pressure : 0.09 inch-H2O

- Air delivery : 2.3 CFM

# 1.6 Appendix 1: GPIO definitions

#### **GPI DEFINITIONS**

| Signal<br>Name | Function   | Description        | During PCIRST# | After<br>PCIRST# | <b>S</b> 1 | <b>S</b> 3 | S4/S5 | Remark |

|----------------|------------|--------------------|----------------|------------------|------------|------------|-------|--------|

| GPIO[0]        | OC0#       | USB OVER CURRENT   | High           | High             | High       | Off        | Off   |        |

| GPIO[2]        | RST_CDROM  | Reset CD-ROM drive | High           | High             | High       | Off        | Off   |        |

| GPIO[3]        | EEDO       | FOR LAN            | In             | In               | Defined    | Off        | Off   |        |

| GPIO[4]        | KBD_US/JP# |                    | In             | In               | Defined    | Off        | Off   |        |

| GPIO[5]        | GPIO5      |                    | In             | In               | Defined    | Off        | Off   |        |

| GPIO[6]        | EXTSMI#    |                    | In             | In               | Defined    | Off        | Off   |        |

| GPIO[7]        | SPDIF      | SPDIF enable       | In             | In               | Defined    | Off        | Off   |        |

| GPIO[8]        | GPIO8      |                    | In             | In               | Defined    | Off        | Off   |        |

| GPIO[9]        | GND        |                    | In             | In               | Defined    | Off        | Off   |        |

| GPIO[10]       | FDD_MODE   |                    | In             | In               | Defined    | Off        | Off   |        |

| GPIO[11]       | SPK_OFF    |                    | In             | In               | Defined    | Off        | Off   |        |

| GPIO[12]       | RS232_OFF# |                    | In             | In               | Defined    | Off        | Off   |        |

| GPIO[13]       | CARD_IN#   |                    | In             | In               | Defined    | Off        | Off   |        |

| GPIO[14]       | CRT_IN#    |                    | In             | In               | Defined    | Off        | Off   |        |

| GPIO[15]       | CARD_ACT   |                    | In             | In               | Defined    | Off        | Off   |        |

# 1.6 Appendix 2: GPIO definitions

## **GPI DEFINITIONS**

Note 1. LCD ID

| LCD_ID2 | LCD_ID1 | LCD_ID0 | Vendor  | PANEL | Description |

|---------|---------|---------|---------|-------|-------------|

| 1       | 1       | 1       | HUYNDAI | 14X13 |             |

|         |         |         |         |       |             |

|         |         |         |         |       |             |

## Note 3. CPU & SDRAM Frequency setting table:

| SW_FS3 | SW_FS2 | SW_FS1 | SW_FS0 | CPU | SDRAM |

|--------|--------|--------|--------|-----|-------|

| 0      | 0      | 0      | 0      | 66  | 100   |

| 0      | 0      | 0      | 1      | 100 | 100   |

| 0      | 0      | 1      | 1      | 133 | 100   |

| 0      | 1      | 0      | 0      | 66  | 133   |

| 0      | 1      | 0      | 1      | 100 | 133   |

| 0      | 1      | 1      | 1      | 133 | 133   |

| 1      | 0      | 0      | 0      | 66  | 66    |

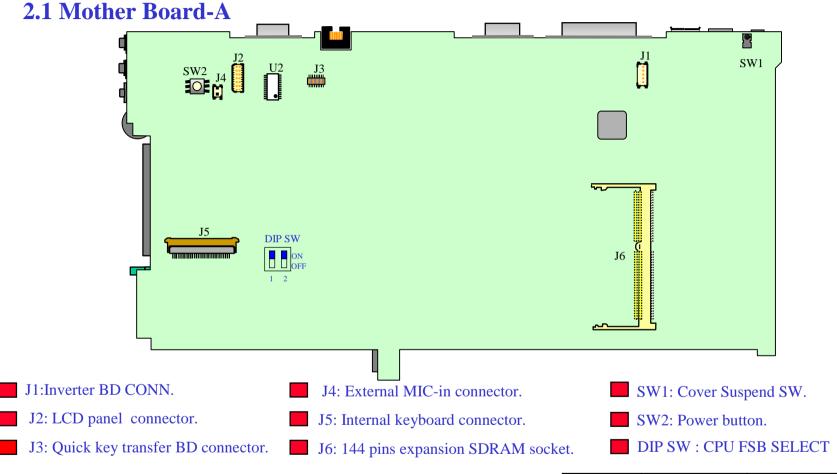

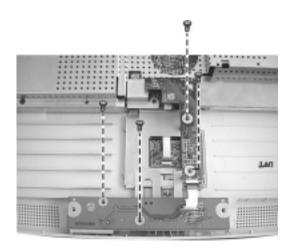

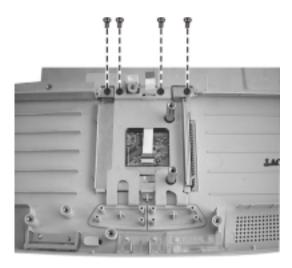

## 2. DEFINITION & LOCATION OF CONNECTORS/SWITCHES

| FSB    | DIP SW /BIT1 | DIP SW /BIT2 |

|--------|--------------|--------------|

| 66MHZ  | OFF          | OFF          |

| 100MHZ | OFF          | ON           |

| 150MHZ | ON           | OFF          |

| 133MHZ | ON           | ON           |

|        |              |              |

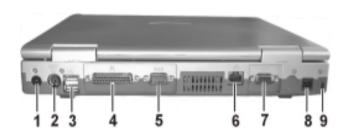

## 2. DEFINITION & LOCATION OF CONNECTORS/SWITCHES

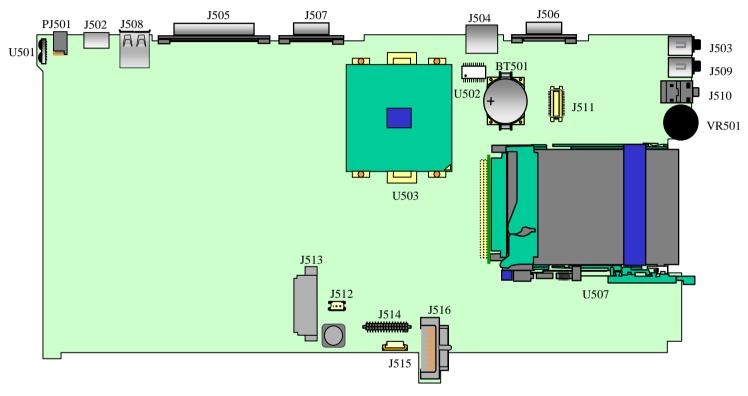

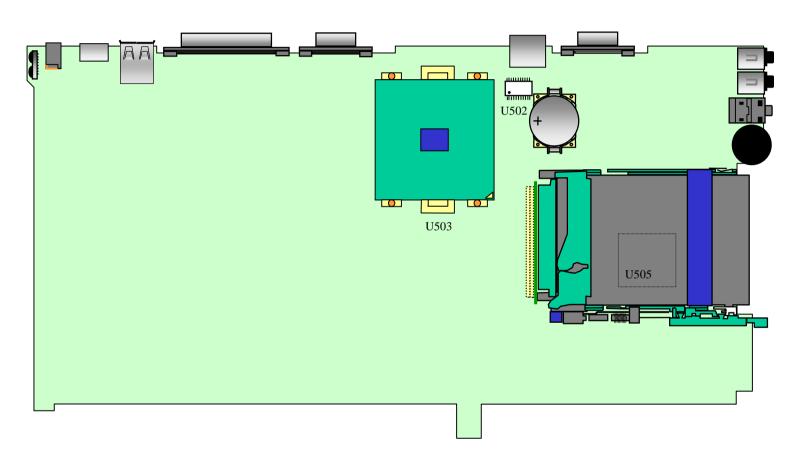

### 2.2 Mother Board-B

J502 :PS2 Mouse/keyboard

J503:Line in Jack.

J504: LAN connect

J505:Parallel Port

J507: VGA Connector.

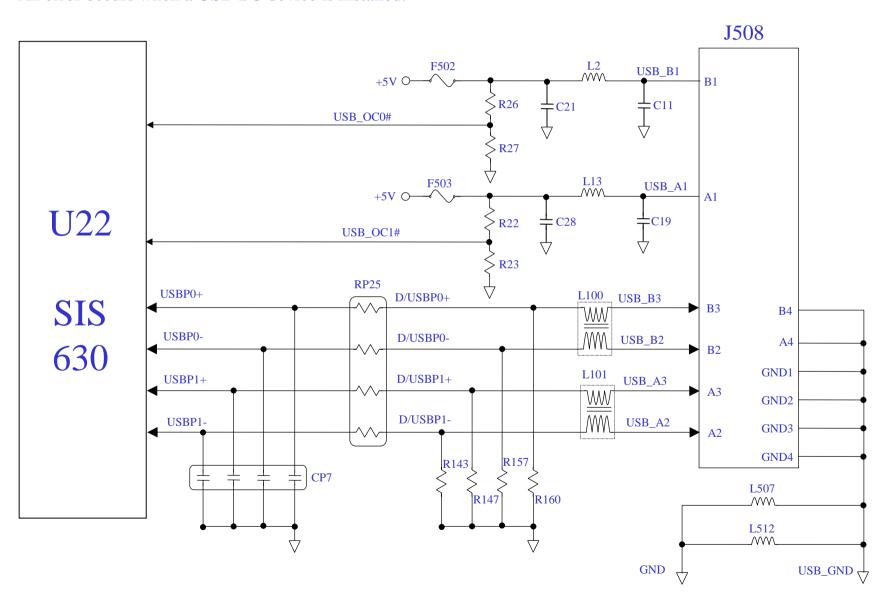

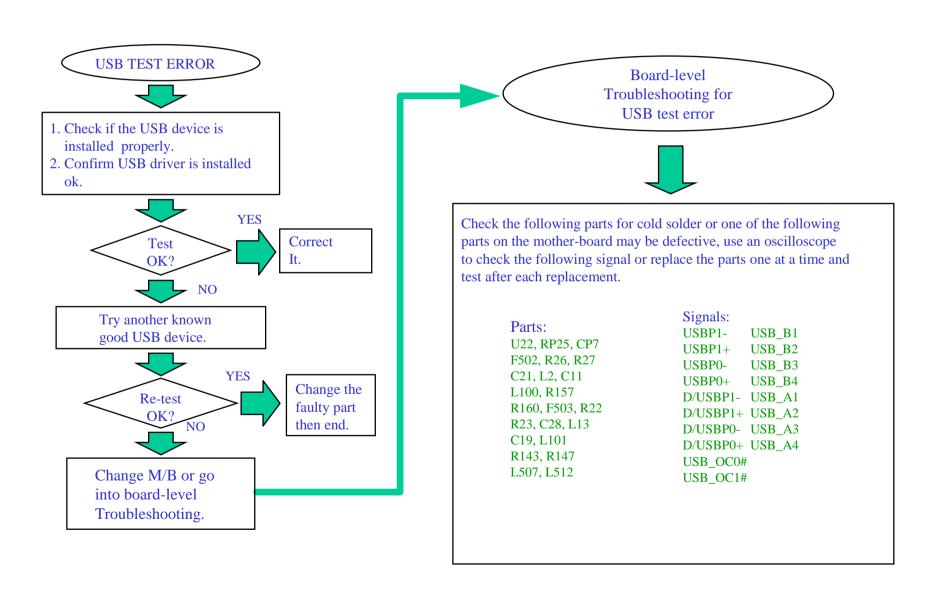

- J508: USB connector.

- U507: PC card socket.

- U503:CPU & CPU Socket.

J511: MODEM transfer board connector

J512: FAN Connector.

J516 :HDD/FDD Connector.

J513: CD-ROM drive connector.

J514:Charger & Touch-Pad connector

J515:Touch-Pad button connector.

BT501: CMOS Battery connector.

VR501: Volume control VR.

## 2. DEFINITION & LOCATION OF CONNECTORS/SWITCHES

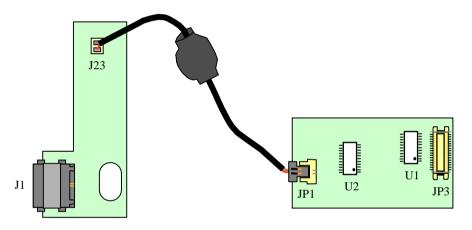

## 2.3 Daughter Board

# MDC/LAN transfer board

- J1: RJ-11 phone jack for internal modem.

- J23: MDC jump wire connector.

- JP1: MDC jump wire connector.

- JP3: Connector 2 for connected MDC/LAN transfer board to M/B.

## 2. DEFINITION & LOCATION OF CONNECTORS/SWITCHES

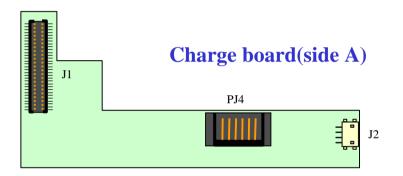

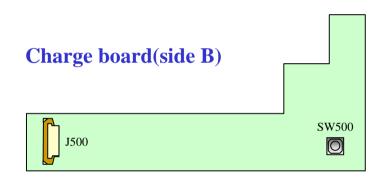

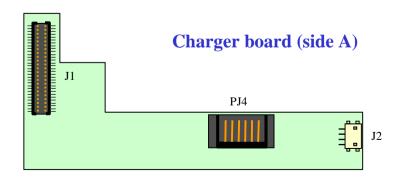

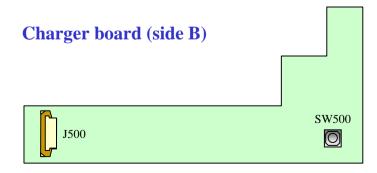

## 2.4 Charger Board

- J1:Charger & Touch-Pad connector to M/B.

- PJ4:Battery pack connector.

- J2: Internal speaker connector.

- J500: Touch-Pad button connector.

- SW500: CMOS Reset

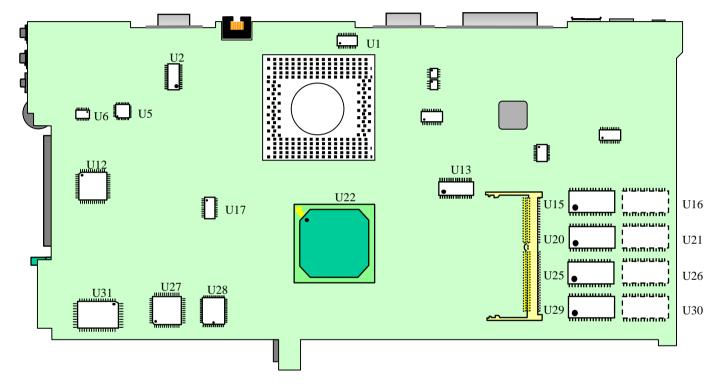

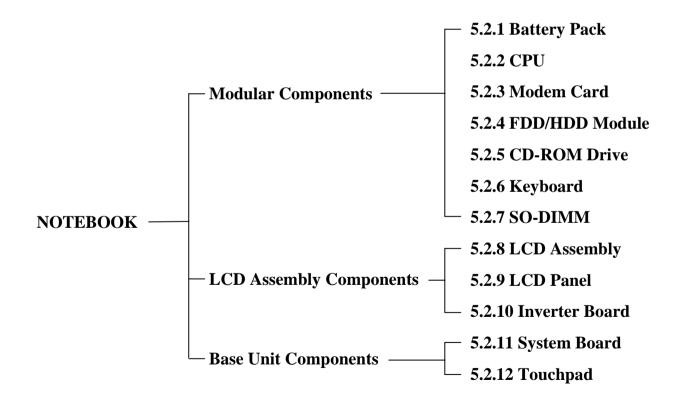

## 3. DEFINITION & LOCATION OF MAJOR COMPONENTS

3.1 Main Board (Side A)

U1: ADM3311ARU RS232/SIO.

- U13: ICS9248-102 Frequency Synthesizer.

- U31:W83626 LPC to ISA.

U15,U20,U25,U29: On board SDAM.

- U2: DS90C363MTD VGA LVD controller.

- U17: TPS2206 PCcard Power switch matrix.

- U5: CS4299 AC'97 CODE. U22: SiS630 single chipset.

- U6: TPA0202 AUDIO AMP.

■ U27: Super IO PC97338VJG.

U12: H8(3434F) universal.

U28: System BIOS.

## 3. DEFINITION & LOCATION OF MAJOR COMPONENTS

3.2 Main Board (SIDE B)

U502: PH163112 LAN Controller.

U503: Socket 370 CPU.

U505: PCI1225PDV PC CARD interface controller.

## 3. DEFINITION & LOCATION OF MAJOR COMPONENTS

## 3.3 Definition Of Daughter Board

#### MDC/LAN transfer board

## 4. PIN DESCRIPTIONS OF MAJOR COMPONENTS

## 4.1 Pentium III/Celeron FC-PGA2 CPU

**Alphabetical Signal Reference**

| Signal Name | I/O       | Signal Description                                                                                                                      |

|-------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| A[35:3]#    | I/O       | The A[35:3]# (Address) signals define a 2 <sup>36</sup> -byte physical memory                                                           |

|             | GTL+      | address space. When ADS# is active, these signals transmit the                                                                          |

|             |           | address of a transaction; when ADS# is inactive, these signals                                                                          |

|             |           | transmit transaction information. These signals must be connected to                                                                    |

|             |           | the appropriate pins/balls of both agents on the system bus. The                                                                        |

|             |           | A[35:24]# signals are protected with the AP1# parity signal,                                                                            |

|             |           | and the A[23:3]# signals are protected with the AP0# parity signal.                                                                     |

|             |           | On the active-to-inactive transition of RESET#, each processor bus                                                                      |

|             |           | agent samples A[35:3]# signals to determine its power-on                                                                                |

|             |           | configuration. See Section 4 of this document and the <i>PentiumII</i>                                                                  |

|             |           | Processor Developer's Manual for details.                                                                                               |

| A20M#       | I         | If the A20M# (Address-20 Mask) input signal is asserted, the                                                                            |

|             | 1.5V      | processor masks physical address bit 20 (A20#) before looking up a                                                                      |

|             | Tolerant  | line in any internal cache and before driving a read/write transaction                                                                  |

|             |           | on the bus. Asserting A20M# emulates the 8086 processor's address                                                                       |

|             |           | wrap-around at the 1-Mbyte boundary. Assertion of A20M# is only                                                                         |

| ADS#        | I/O       | supported in Real mode.                                                                                                                 |

| ADS#        | GTL+      | The ADS# (Address Strobe) signal is asserted to indicate the validity of a transaction address on the A[35:3]# signals. Both bus agents |

|             | OIL+      | observe the ADS# activation to begin parity checking, protocol                                                                          |

|             |           | checking, address decode, internal snoop or deferred reply ID match                                                                     |

|             |           | operations associated with the new transaction. This signal must be                                                                     |

|             |           | connected to the appropriate pins/balls on both agents on the system                                                                    |

|             |           | bus.                                                                                                                                    |

| AERR#       | I/O       | The AERR# (Address Parity Error) signal is observed and driven by                                                                       |

|             | GTL+      | both system bus agents, and if used, must be connected to the                                                                           |

|             |           | appropriate pins/balls of both agents on the system bus. AERR#                                                                          |

|             |           | observation is optionally enabled during power-on configuration; if                                                                     |

|             |           | enabled, a valid assertion of AERR# aborts the current transaction.                                                                     |

|             |           | If AERR# observation is disabled during power-on configuration, a                                                                       |

|             |           | central agent may handle an assertion of AERR# as appropriate to the                                                                    |

|             |           | error handling architecture of the system.                                                                                              |

| AP[1:0]#    | I/O       | The AP[1:0]# (Address Parity) signals are driven by the request                                                                         |

|             | GTL+      | initiator along with ADS#, A[35:3]#, REQ[4:0]# and RP#. AP1#                                                                            |

|             |           | covers A[35:24]#. AP0# covers A[23:3]#. A correct parity signal is                                                                      |

|             |           | high if an even number of covered signals are low and low if an odd                                                                     |

|             |           | number of covered signals are low. This allows parity to be high when                                                                   |

|             |           | all the covered signals are high. AP[1:0]# should be connected to the                                                                   |

| DCI IZ      | т         | appropriate pins/balls on both agents on the system bus.                                                                                |

| BCLK        | I<br>2.5V | The BCLK (Bus Clock) signal determines the system bus frequency.                                                                        |

|             |           | Both system bus agents must receive this signal to drive their outputs                                                                  |

|             | Toterant  | and latch their inputs on the BCLK rising edge. All external timing parameters are specified with respect to the BCLK signal.           |

|             |           | parameters are specified with respect to the BCLK signal.                                                                               |

| Signal Name | I/O          | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BERR#       | I/O<br>GTL+  | The BERR# (Bus Error) signal is asserted to indicate an unrecoverable error without a bus protocol violation. It may be driven by either system bus agent and must be connected to the appropriate pins/balls of both agents, if used. However, the mobile Pentium III processors do not observe assertions of the BERR# signal.  BERR# assertion conditions are defined by the system configuration. Configuration options enable the BERR# driver as follows:  • Enabled or disabled  • Asserted optionally for internal errors along with IERR#  • Asserted optionally by the request initiator of a bus transaction after it observes an error  • Asserted by any bus agent when it observes an error in a bus transaction                                                                                                                       |

| BINIT#      | I/O-<br>GTL+ | The BINIT# (Bus Initialization) signal may be observed and driven by both system bus agents and must be connected to the appropriate pins/balls of both agents, if used. If the BINIT# driver is enabled during the power-on configuration, BINIT# is asserted to signal any bus condition that prevents reliable future information.  If BINIT# is enabled during power-on configuration, and BINIT# is sampled asserted, all bus state machines are reset and any data which was in transit is lost. All agents reset their rotating ID for bus arbitration to the state after reset, and internal count information is lost. The L1 and L2 caches are not affected.  If BINIT# is disabled during power-on configuration, a central agent may handle an assertion of BINIT# as appropriate to the Machine Check Architecture (MCA) of the system. |

| BNR#        | I/O-<br>GTL+ | The BNR# (Block Next Request) signal is used to assert a bus stall by any bus agent that is unable to accept new bus transactions. During a bus stall, the current bus owner cannot issue any new transactions. Since multiple agents may need to request a bus stall simultaneously, BNR# is a wired-OR signal that must be connected to the appropriate pins/balls of both agents on the system bus. In order to avoid wire-OR glitches associated with simultaneous edge transitions driven by multiple drivers, BNR# is activated on specific clock edges and sampled on specific clock edges.                                                                                                                                                                                                                                                   |

| BP[3:2]#    | I/O<br>GTL+  | The BP[3:2]# (Breakpoint) signals are the System Support group Breakpoint signals. They are outputs from the processor that indicate the status of breakpoints.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BPM[1:0]#   | I/O<br>GTL+  | The BPM[1:0]# (Breakpoint Monitor) signals are breakpoint and performance monitor signals. They are outputs from the processor that indicate the status of breakpoints and programmable counters used for monitoring processor performance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

## 4. PIN DESCRIPTIONS OF MAJOR COMPONENTS

## 4.1 Pentium III/Celeron FC-PGA2 CPU

**Alphabetical Signal Reference**

| Signal Name | I/O      | Signal Description                                                                                        |

|-------------|----------|-----------------------------------------------------------------------------------------------------------|

| BPRI#       | I        | The BPRI# (Bus Priority Request) signal is used to arbitrate for                                          |

|             | GTL+     | ownership of the system bus. It must be connected to the appropriate                                      |

|             |          | pins/balls on both agents on the system bus. Observing BPRI# active                                       |

|             |          | (as asserted by the priority agent) causes the processor to stop issuing                                  |

|             |          | new requests, unless such requests are part of an ongoing locked                                          |

|             |          | operation. The priority agent keeps BPRI# asserted until all of its                                       |

|             |          | requests are completed and then releases the bus by deasserting                                           |

|             |          | BPRI#.                                                                                                    |

| BREQ0#      | I/O      | The BREQ0# (Bus Request) signal is a processor Arbitration Bus                                            |

|             | GTL+     | signal. The processor indicates that it wants ownership of the system bus by asserting the BREQ0# signal. |

|             |          | During power-up configuration, the central agent must assert the                                          |

|             |          | BREQ0# bus signal. The processor samples BREQ0# on the active-                                            |

|             |          | to-inactive transition of RESET#.                                                                         |

| BSEL[1:0]   | I        | The BSEL[1:0] (Select Processor System Bus Speed) signal is used to                                       |

|             |          | configure the processor for the system bus frequency. Table 38 shows                                      |

|             | Tolerant | the encoding scheme for BSEL[1:0]. The only supported system bus                                          |

|             |          | frequency for the mobile Pentium III processor is 100 MHz. If                                             |

|             |          | another frequency is used or if the BSEL[1:0] signals are not driven                                      |

|             |          | with "1" then the processor is not guaranteed to function properly.                                       |

|             |          | BSEL[1:0] Encoding                                                                                        |

|             |          | BSEL[1:0] System Bus Frequency 00 66 MHz                                                                  |

|             |          | 00 06 MHZ<br>01 100 MHz                                                                                   |

|             |          | 10 Reserved                                                                                               |

|             |          | 11 133 MHz                                                                                                |

| CLKREF      | Analog   |                                                                                                           |

| CLIKICI     | Tinalog  | reference voltage to define the trip point for the BCLK signal. This                                      |

|             |          | signal should be connected to a resistor divider to generate 1.25V                                        |

|             |          | from the 2.5-V supply.                                                                                    |

| CMOSREF     | Analog   | The CMOSREF (CMOS Reference Voltage) signal provides a DC                                                 |

|             |          | level reference voltage for the CMOS input buffers. A voltage divider                                     |

|             |          | should be used to divide a stable voltage plane (e.g., 2.5V or 3.3V).                                     |

|             |          | This signal must be provided with a DC voltage that meets the                                             |

|             |          | VCMOSREF specification from Table 13.                                                                     |

| D[63:0]#    | I/O      | The D[63:0]# (Data) signals are the data signals. These signals                                           |

|             | GTL+     | provide a 64-bit data path between both system bus agents, and must                                       |

|             |          | be connected to the appropriate pins/balls on both agents. The data                                       |

|             |          | driver asserts DRDY# to indicate a valid data transfer.                                                   |

| Signal Name | I/O                                      | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DBSY#       | I/O-<br>GTL+                             | The DBSY# (Data Bus Busy) signal is asserted by the agent responsible for driving data on the system bus to indicate that the data bus is in use. The data bus is released after DBSY# is deasserted. This signal must be connected to the appropriate pins/balls on both agents on the system bus.                                                                                                                                                                                     |

| DEFER#      | I<br>GTL+                                | The DEFER# (Defer) signal is asserted by an agent to indicate that the transaction cannot be guaranteed in-order completion. Assertion of DEFER# is normally the responsibility of the addressed memory agent or I/O agent. This signal must be connected to the appropriate pins/balls on both agents on the system bus.                                                                                                                                                               |

| DEP[7:0]#   | I/O<br>GTL+                              | The DEP[7:0]# (Data Bus ECC Protection) signals provide optional ECC protection for the data bus. They are driven by the agent responsible for driving D[63:0]#, and must be connected to the appropriate pins/balls on both agents on the system bus if they are used. During power-on configuration, DEP[7:0]# signals can be enabled for ECC checking or disabled for no checking.                                                                                                   |

| DRDY#       | I/O<br>GTL+                              | The DRDY# (Data Ready) signal is asserted by the data driver on each data transfer, indicating valid data on the data bus. In a multicycle data transfer, DRDY# can be deasserted to insert idle clocks. This signal must be connected to the appropriate pins/balls on both agents on the system bus.                                                                                                                                                                                  |

| EDGCTRLP    | Analog                                   | The EDGCTRLP (Edge Rate Control) signal is used to configure the edge rate of the GTL+ output buffers. Connect the signal to VSS with a $110-\Omega$ , 1% resistor.                                                                                                                                                                                                                                                                                                                     |

| FERR#       | O<br>1.5V<br>Tolerant<br>Open-<br>drain) | The FERR# (Floating-point Error) signal is asserted when the processor detects an unmasked floating-point error. FERR# is similar to the ERROR# signal on the Intel 387 coprocessor, and it is included for compatibility with systems using DOS-type floating-point error reporting.                                                                                                                                                                                                   |

| FLUSH#      | I<br>1.5V<br>Tolerant                    | When the FLUSH# (Flush) input signal is asserted, the processor writes back all internal cache lines in the Modified state and invalidates all internal cache lines. At the completion of a flush operation, the processor issues a Flush Acknowledge transaction. The processor stops caching any new data while the FLUSH# signal remains asserted.  On the active-to-inactive transition of RESET#, each processor bus agent samples FLUSH# to determine its power-on configuration. |

## 4. PIN DESCRIPTIONS OF MAJOR COMPONENTS

## 4.1 Pentium III/Celeron FC-PGA2 CPU

**Alphabetical Signal Reference**

| Signal Name | I/O      | Signal Description                                                       |

|-------------|----------|--------------------------------------------------------------------------|

| GHI#        | I        | The GHI# signal controls which operating mode bus ratio is selected      |

|             | 1.5V     | in a mobile Pentium III processor featuring Intel SpeedStep              |

|             | Tolerant | technology. On the processor featuring Intel SpeedStep technology,       |

|             |          | this signal is latched when BCLK restarts in Deep Sleep state and        |

|             |          | determines which of two bus ratios is selected for operation. This       |

|             |          | signal is ignored when the processor is not in the Deep Sleep state.     |

|             |          | This signal is a "Don't Care" on processors that do not feature Intel    |

|             |          | SpeedStep technology. This signal has an on-die pull-up to VccT and      |

|             |          | should be driven with an Open-drain driver with no external pull-up.     |

| HIT#, HITM# | I/O      | The HIT# (Snoop Hit) and HITM# (Hit Modified) signals convey             |

|             | GTL+     | transaction snoop operation results, and must be connected to the        |

|             |          | appropriate pins/balls on both agents on the system bus.                 |

|             |          | Either bus agent can assert both HIT# and HITM# together to indicate     |

|             |          | that it requires a snoop stall, which can be continued by reasserting    |

|             |          | HIT# and HITM# together.                                                 |

| IERR#       | О        | The IERR# (Internal Error) signal is asserted by the processor as the    |

|             | 1.5V     | result of an internal error. Assertion of IERR# is usually accompanied   |

|             |          | by a SHUTDOWN transaction on the system bus.                             |

|             | Open-    | This transaction may optionally be converted to an external error        |

|             | drain    | signal (e.g., NMI) by system logic. The processor will keep IERR#        |

|             |          | asserted until it is handled in software or with the assertion of        |

|             | _        | RESET#, BINIT, or INIT#.                                                 |

| IGNNE#      | I        | The IGNNE# (Ignore Numeric Error) signal is asserted to force the        |

|             | 1.5V     | processor to ignore a numeric error and continue to execute non-         |

|             | Tolerant | ,                                                                        |

|             |          | processor freezes on a non-control floating-point instruction if a       |

|             |          | previous instruction caused an error. IGNNE# has no affect when the      |

| TA ITEM     | ,        | NE bit in control register 0 (CR0) is set.                               |

| INIT#       | I        | The INIT# (Initialization) signal is asserted to reset integer registers |

|             | 1.5V     | inside the processor without affecting the internal (L1 or L2) caches    |

|             | Tolerant | or the floating-point registers. The processor begins execution at the   |

|             |          | power-on reset vector configured during power-on configuration. The      |

|             |          | processor continues to handle snoop requests during INIT# assertion.     |

|             |          | INIT# is an asynchronous input.                                          |

|             |          | If INIT# is sampled active on RESET#'s active-to-inactive transition,    |

|             | 1        | then the processor executes its built-in self test (BIST).               |

| Signal Name | I/O                   | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTR        | I<br>1.5V<br>Tolerant | The INTR (Interrupt) signal indicates that an external interrupt has been generated. INTR becomes the LINTO signal when the APIC is enabled. The interrupt is maskable using the IF bit in the EFLAGS register. If the IF bit is set, the processor vectors to the interrupt handler after completing the current instruction execution. Upon recognizing the interrupt request, the processor issues a single Interrupt Acknowledge (INTA) bus transaction. INTR must remain active until the INTA bus transaction to guarantee its recognition.                                                                                                                                               |

| LINT[1:0]   | I<br>1.5V<br>Tolerant | The LINT[1:0] (Local APIC Interrupt) signals must be connected to the appropriate pins/balls of all APIC bus agents, including the processor and the system logic or I/O APIC component. When APIC is disabled, the LINT0 signal becomes INTR, a maskable interrupt request signal, and LINT1 becomes NMI, a non-maskable interrupt. INTR and NMI are backward compatible with the same signals for the Pentium processor. Both signals are asynchronous inputs. Both of these signals must be software configured by programming the APIC register space to be used either as NMI/INTR or LINT[1:0] in the BIOS. If the APIC is enabled at reset, then LINT[1:0] is the default configuration. |

| LOCK#       | I/O<br>GTL+           | The LOCK# (Lock) signal indicates to the system that a sequence of transactions must occur atomically. This signal must be connected to the appropriate pins/balls on both agents on the system bus. For a locked sequence of transactions, LOCK# is asserted from the beginning of the first transaction through the end of the last transaction.  When the priority agent asserts BPRI# to arbitrate for bus ownership, it waits until it observes LOCK# deasserted. This enables the processor to retain bus ownership throughout the bus locked operation and guarantee the atomicity of lock.                                                                                              |

| NMI         |                       | The NMI (Non-Maskable Interrupt) indicates that an external interrupt has been generated. NMI becomes the LINT1 signal when the APIC is disabled. Asserting NMI causes an interrupt with an internally supplied vector value of 2. An external interrupt-acknowledge transaction is not generated. If NMI is asserted during the execution of an NMI service routine, it remains pending and is recognized after the IRET is executed by the NMI service routine. At most, one assertion of NMI is held pending. NMI is rising edge sensitive.                                                                                                                                                  |

## 4. PIN DESCRIPTIONS OF MAJOR COMPONENTS

## 4.1 Pentium III/Celeron FC-PGA2 CPU

**Alphabetical Signal Reference**

| Signal Name | I/O      | Signal Description                                                       |

|-------------|----------|--------------------------------------------------------------------------|

| PICCLK      | I        | The PICCLK (APIC Clock) signal is an input clock to the processor        |

| TICCEIL     | 2.5V     | and system logic or I/O APIC that is required for operation of the       |

|             |          | processor, system logic, and I/O APIC components on the APIC bus.        |

| PICD[1:0]   | I/O      | The PICD[1:0] (APIC Data) signals are used for bi-directional serial     |

| 1102[1.0]   | 1.5V     | message passing on the APIC bus. They must be connected to the           |

|             |          | appropriate pins/balls of all APIC bus agents, including the processor   |

|             | Open-    | and the system logic or I/O APIC components. If the PICD0 signal is      |

|             | drain    | sampled low on the active-to-inactive transition of the RESET#           |

|             | urum.    | signal, then the APIC is hardware disabled.                              |

| PLL1, PLL2  | Analog   | 8 7                                                                      |

| ,           |          | required for the internal PLL. See Section 3.2.2 for a description of    |

|             |          | the analog decoupling circuit.                                           |

| PRDY#       | 0        | The PRDY# (Probe Ready) signal is a processor output used by             |

|             | GTL+     | debug tools to determine processor debug readiness.                      |

| PREQ#       | ī        | The PREQ# (Probe Request) signal is used by debug tools to request       |

|             | 1.5V     | debug operation of the processor.                                        |